# Теория дискретных устройств

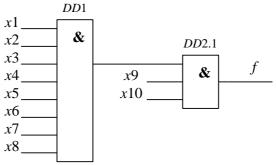

# МИНИСТЕРСТВО ОБРАЗОВАНИЯ РЕСПУБЛИКИ БЕЛАРУСЬ УЧРЕЖДЕНИЕ ОБРАЗОВАНИЯ «БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ТРАНСПОРТА»

Кафедра автоматики и телемеханики

К. А. БОЧКОВ, Ю. Ф. БЕРЕЗНЯЦКИЙ

### ТЕОРИЯ ДИСКРЕТНЫХ УСТРОЙСТВ

Допущено Министерством образования Республики Беларусь в качестве учебного пособия для студентов учреждений, обеспечивающих получение высшего образования по транспортным специальностям

УДК 004.31 (075.8) ББК 22.176+32.965.6 Б86

Р е ц е н з е н т ы: заведующий лабораторией логического проектирования Объединенного института проблем информатики Национальной академии наук Беларуси д-р техн. наук, профессор  $\Pi$ . H. Euбило;

кафедра информатики факультета радиофизики и электроники учреждения образования «Белорусский государственный университет», канд. техн. наук, доцент  $\Gamma$ . K. Aфанасьев.

#### Бочков, К. А.

Б86 Теория дискретных устройств: учеб. пособие / К. А. Бочков, Ю. Ф. Березняцкий; М-во образования Респ. Беларусь, Белорус. гос. ун-т трансп. – Гомель: БелГУТ, 2007. – 162 с. ISBN 978-986-468-327-0

Рассматриваются вопросы создания схемных реализаций компонентов систем автоматики, телемеханики и связи, предлагаются варианты увязки созданных компонентов для реализации действующих систем с применением интегральных микросхем.

Предназначено для студентов высших и среднеспециальных учебных заведений, обучающихся по специальности «Автоматика, телемеханика и связь на железнодорожном транспорте», в качестве методического руководства по построению систем автоматики, телемеханики и связи на основе интегральных микросхем. Также будет полезно студентам при выполнении курсового проекта.

УДК 004.31 (075.8) ББК 22.176+32.965.6

© Оформление. УО «БелГУТ», 2007

Данное пособие написано в соответствии с программой для обучающихся «Автоматика, ПО специальности телемеханика и связь на железнодорожном транспорте» и содержит основные сведения по синтезу таких узлов систем автоматики и как шифраторы, дешифраторы, преобразователи телемеханики, кодов, мультиплексоры, демультиплексоры, счетчики импульсов, делители частоты, двоичные сумматоры, различные регистры. Для всех указанных дискретных устройств построены диаграммы (диаграммы состояний), способствующие анализу функционирования дискретных устройств.

Во втором разделе приводится методика и примеры синтеза компонентов систем автоматики и телемеханики на базе асинхронных и синхронных мультиплексоров, что в ряде случаев позволяет сократить количество используемых для реализации схемы корпусов интегральных микросхем.

Раздел четыре пособия содержит основные положения по анализу комбинационных и многотактных дискретных схем. Здесь рассмотрен анализ электрических схем дискретных устройств как с фиксацией воздействия (релейных), так и без фиксации воздействия (триггерных).

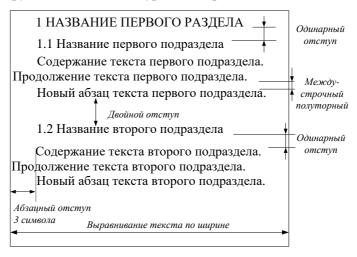

Проработка разделов пять и шесть пособия позволит студенту технически грамотно и квалифицированно оформить принципиальные схемы и пояснительную записку к выполняемому курсовому проекту.

В приложениях к пособию приведены условные обозначения наиболее часто используемых цифровых интегральных микросхем, основные виды надписей на текстовых документах и схемах, сведения о кварцевых резонаторах, применяемых в курсовом проекте по дисциплине «Теория дискретных устройств».

Пособие рассчитано на студентов и специалистов, имеющих начальные знания в теории дискретных устройств, поэтому в нем опущены отдельные детали.

## **1** СИНТЕЗ КОМПОНЕНТОВ СИСТЕМ АВТОМАТИКИ И ТЕЛЕМЕХАНИКИ

#### 1.1 ШИФРАТОРЫ

**Шифратор** — комбинационное дискретное устройство, позволяющее получить на выходе кодовую комбинацию, соответствующую номеру одного из десятичных входов, на котором появилась логическая единица [1].

Шифраторы широко применяются для ввода информации в устройства системы. Классический дискретные И использования шифраторов – простая клавиатура или пультманипулятор, в которых при нажатии оператором определенной управления) (кнопки на выходе соответствующее, уникальное для данной клавиши, кодовое слово. Также шифраторы часто используются в системах телесигнализации при сборе информации о состоянии объектов. В данном случае двухстабильного объекта каждого подключается ко входам шифратора. Изменение или подтверждение состояния конкретного объекта выражается в виде кодовой комбинации, состоящей из двух частей адресной и информационной. Адресная часть получается как код на выходе шифратора, а информационная может быть представлена в виде логической единицы или логического нуля в дополнительном разряде, зависимости ОТ состояния объекта сигнализации (двигатель

включен/выключен, лампа горит/погашена, стрелка в минусовом/плюс овом положении, контакт замкнут/разомкнут и т. п.).

Синтез шифратора, как и большинства других дискретных устройств, может быть выполнен по его таблице истинности. В таблице отражаются все возможные входы шифратора и все состояния выходов, им соответствующие. В таблице 1.1 в качестве примера показана таблица истинности шифратора для перевода десятичных чисел от 0 до 6 в двоичный код «3a + 2» [1].

Функции выходов шифратора с использованием свойства независимости входов и выходов могут быть получены как дизьюнкция тех входов, на которых значение рассматриваемого выхода равно единице. В аналитическом виде получим:  $Y1 = X5 \lor X6$ ;  $Y2 = X2 \lor \lor X3 \lor X4$ ;  $Y3 = X1 \lor X4 \lor X6$ ;  $Y4 = X0 \lor X3 \lor X4$ ;  $Y5 = X1 \lor X3 \lor X5$ .

| Таблина 1.1 – <b>Таблина истинности шифратора в кол «За</b> + 2 | Таблипа | 1.1 – Таблица истинности шифратора в код «3 | a + 2» |

|-----------------------------------------------------------------|---------|---------------------------------------------|--------|

|-----------------------------------------------------------------|---------|---------------------------------------------|--------|

| Десятичное<br>число | Код «3а+2» |            |            | Десятичное<br>число |            | Код | ц «За +    | - 2»       |            |            |            |

|---------------------|------------|------------|------------|---------------------|------------|-----|------------|------------|------------|------------|------------|

| Xi                  | <i>Y</i> 1 | <i>Y</i> 2 | <i>Y</i> 3 | <i>Y</i> 4          | <i>Y</i> 5 | Xi  | <i>Y</i> 1 | <i>Y</i> 2 | <i>Y</i> 3 | <i>Y</i> 4 | <i>Y</i> 5 |

| 0                   | 0          | 0          | 0          | 1                   | 0          | 4   | 0          | 1          | 1          | 1          | 0          |

| 1                   | 0          | 0          | 1          | 0                   | 1          | 5   | 1          | 0          | 0          | 0          | 1          |

| 2                   | 0          | 1          | 0          | 0                   | 0          | 6   | 1          | 0          | 1          | 0          | 0          |

| 3                   | 0          | 1          | 0          | 1                   | 1          | 0   | 1          | U          | 1          | U          | U          |

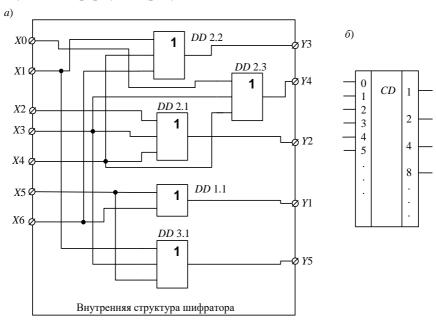

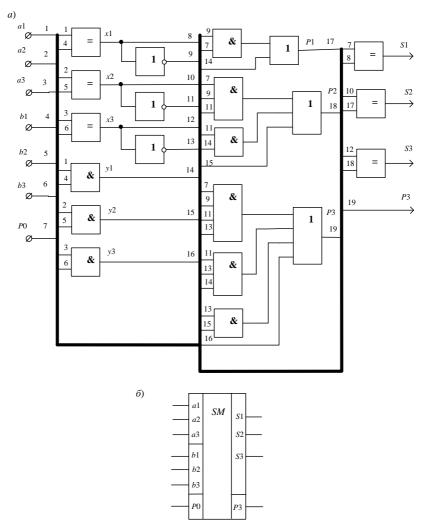

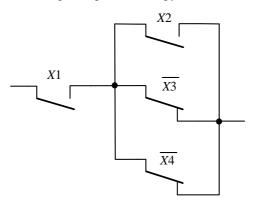

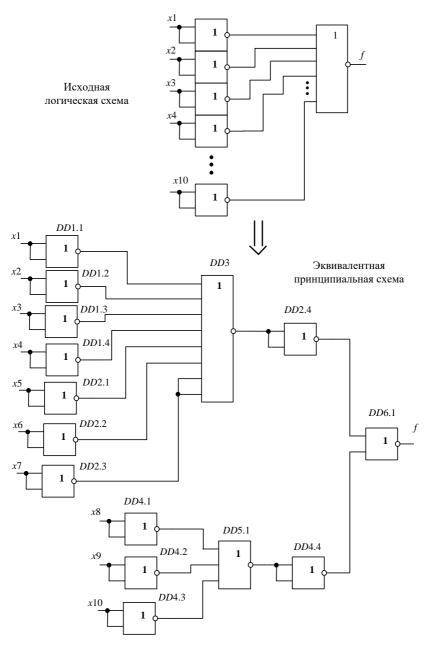

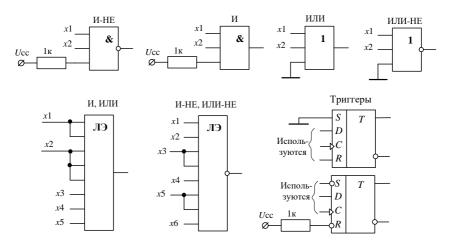

Построим схему шифратора в базисе «И-ИЛИ-НЕ» [1] по полученным формулам (рисунок 1.1, a).

Рисунок 1.1 – Схема шифратора (a) и его условное обозначение  $(\delta)$

Шифратор имеет условное графическое обозначение, показанное на рисунке 1.1,  $\delta$ .

Рассмотрим пример построения шифратора, заданного таблицей 1.2 и предназначенного для получения кода «2 из 5» с использованием элементов базиса «И-НЕ» [1] для чисел десятичного кода от 8 до 14.

Поскольку код «2 из 5» определен для десятичных чисел от 0 до 9, а нам требуется использовать числа больше 9, то применим двоично-десятичный принцип построения шифратора. Тогда каждое десятичное число будет представлено соответствующей ему кодовой комбинацией из единиц и десятков, что и отражено в таблице 1.2.

| Десятич<br>ные |            | Код «2 из 5» |            |            |            |            |            |         |            |     |

|----------------|------------|--------------|------------|------------|------------|------------|------------|---------|------------|-----|

| числа          |            |              | десятки    |            |            |            |            | единицы | I          |     |

| Xi             | <i>Y</i> 1 | <i>Y</i> 2   | <i>Y</i> 3 | <i>Y</i> 4 | <i>Y</i> 5 | <i>Y</i> 6 | <i>Y</i> 7 | Y8      | <i>Y</i> 9 | Y10 |

| 8              | 1          | 1            | 0          | 0          | 0          | 1          | 0          | 0       | 1          | 0   |

| 9              | 1          | 1            | 0          | 0          | 0          | 0          | 1          | 0       | 0          | 1   |

| 10             | 0          | 1            | 1          | 0          | 0          | 1          | 1          | 0       | 0          | 0   |

| 11             | 0          | 1            | 1          | 0          | 0          | 0          | 1          | 1       | 0          | 0   |

| 12             | 0          | 1            | 1          | 0          | 0          | 0          | 0          | 1       | 1          | 0   |

| 13             | 0          | 1            | 1          | 0          | 0          | 0          | 0          | 0       | 1          | 1   |

| 14             | 0          | 1            | 1          | 0          | 0          | 1          | 0          | 0       | 0          | 1   |

Таблица 1.2 – Таблица истинности шифратора в код «2 из 5»

Запишем формулы связи между входами и выходами и преобразуем их с использованием закона двойственности к виду, удобному для представления в базисе «И-НЕ»:

$$Y1 = X8 \lor X9 = \overline{X}8\overline{X}9 = \overline{X}8 \mid \overline{X}9$$

;

$$Y2 = X8 \lor X9 \lor ... \lor X14 = 1; \ Y3 = X10 \lor X11 \lor X12 \lor X13 \lor X14 =$$

=  $\overline{X}10 | \overline{X}11 | \overline{X}12 | \overline{X}13 | \overline{X}14; \ Y4 = 0; \ Y5 = 0; \ Y6 = X8 \lor X10 \lor X14 =$

=  $\overline{X}8 | \overline{X}10 | \overline{X}14; \ Y7 = \overline{X}9 | \overline{X}10 | \overline{X}11; \ Y8 = \overline{X}11 | \overline{X}12; \ Y9 = \overline{X}8 | \overline{X}12 | \overline{X}13;$

$Y10 = \overline{X}9 | \overline{X}13 | \overline{X}14.$

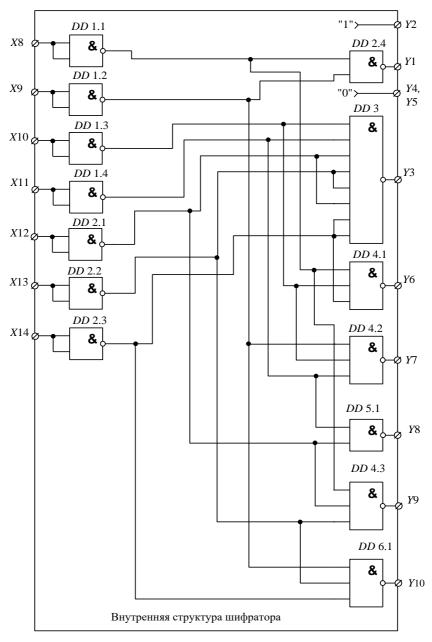

Схема шифратора представлена на рисунке 1.2.

Рассмотрим далее примеры построения дешифраторов – устройств по действию обратных шифраторам.

#### 1.2 ДЕШИФРАТОРЫ

Дешифратор — комбинационное дискретное устройство, позволяющее получить на одном из десятичных выходов логическую

единицу, эквивалентную поданному на входы двоичному коду [1].

Существует также разновидность дешифраторов, у которых логическая единица образуется не на одном, а на нескольких выходах.

Рисунок 1.2 – Схема шифратора для кода «2 из 5»

Они ближе к преобразователям кодов по структуре, чем к дешифраторам, но в технической (справочной) литературе их называют дешифраторами [2, 3]. Это так называемые преобразователи двоичного кода В семисегментный семисегментного индикатора). Также существуют дешифраторы, позволяющие преобразовать двоичный код в код матричного индикатора, образующего числа или буквы в виде совокупности точек матричного поля.

Дешифраторы широко применяются для вывода информации из дискретных устройств и систем. Основная функция дешифраторов заключается в том, чтобы информация, выдаваемая цифровыми устройствами, была понятна человеку, выполняющему обслуживание цифровой системы либо устройства.

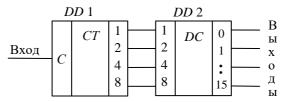

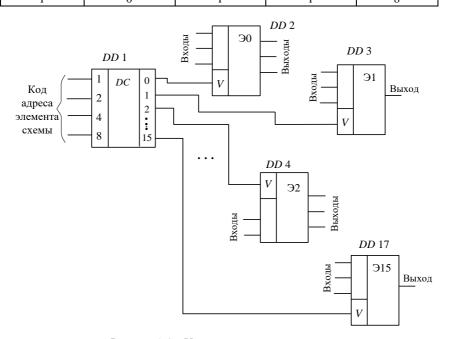

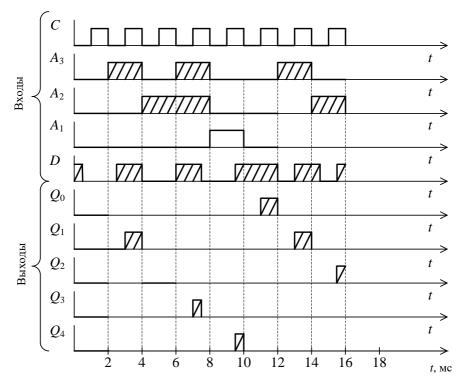

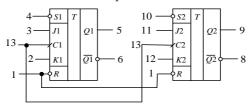

Дешифраторы являются компонентами цифровых распределителей в совокупности со счетчиками импульсов (рисунок 1.3).

Рисунок 1.3 — Реализация распределителя с применением дешифратора

При использовании суммирующего счетчика логическая единица будет появляться по очереди на выходных разрядах 0, 1, 2 и т. д. до 15, а в случае применения вычитающего счетчика логическая единица будет появляться в обратном порядке (по такому принципу строятся так называемые распределители прямого и обратного ходов).

Часто дешифраторы в системах автоматики и телемеханики и других микропроцессорных системах применяются для выбора элемента схемы, который должен выполнить необходимую функцию (рисунок 1.4).

К выходам дешифратора подключены различные дискретные устройства (Э0 – Э15). В зависимости от того, какой код подан на входы дешифратора, выбирается тот дискретный компонент  $\ni i$  схемы, работа которого в данный момент разрешена. Это определяется сигналом логической единицы на входе разрешения

записи (работы) "V" соответствующего компонента, выдаваемым дешифратором.

В таблице истинности дешифратора, по отношению к таблице истинности шифратора, входы и выходы меняются местами. В таблице  $1.3\,$  в качестве примера показана таблица истинности дешифратора, позволяющего преобразовать двоичные слова кода «с избытком 3» в десятичные числа от 0 до 8.

|            |                              |            | _          |    |  |  |  |  |

|------------|------------------------------|------------|------------|----|--|--|--|--|

|            | Кодовые слова «с избытком 3» |            |            |    |  |  |  |  |

| <i>Y</i> 1 | Y2                           | <i>Y</i> 3 | <i>Y</i> 4 | Zi |  |  |  |  |

| 0          | 0                            | 1          | 1          | 0  |  |  |  |  |

| 0          | 1                            | 0          | 0          | 1  |  |  |  |  |

| 0          | 1                            | 0          | 1          | 2  |  |  |  |  |

| 0          | 1                            | 1          | 0          | 3  |  |  |  |  |

| 0          | 1                            | 1          | 1          | 4  |  |  |  |  |

| 1          | 0                            | 0          | 0          | 5  |  |  |  |  |

| 1          | 0                            | 0          | 1          | 6  |  |  |  |  |

|            |                              |            |            |    |  |  |  |  |

Таблица 1.3 – Таблица истинности дешифратора из кода «с избытком 3»

Рисунок 1.4 – Узел системы телемеханики

Функции выходов дешифратора могут быть получены как конъюнкция переменных соответствующих кодовых слов:

$$Z0 = \overline{Y}1\overline{Y}2Y3Y4; Z1 = \overline{Y}1Y2\overline{Y}3\overline{Y}4; Z2 = \overline{Y}1Y2\overline{Y}3Y4; Z3 = \overline{Y}1Y2Y3\overline{Y}4;$$

$Z4 = \overline{Y}1Y2Y3Y4; Z5 = Y1\overline{Y}2\overline{Y}3\overline{Y}4; Z6 = Y1\overline{Y}2\overline{Y}3Y4; Z7 = Y1\overline{Y}2Y3\overline{Y}4;$

$Z8 = Y1\overline{Y}2Y3Y4.$

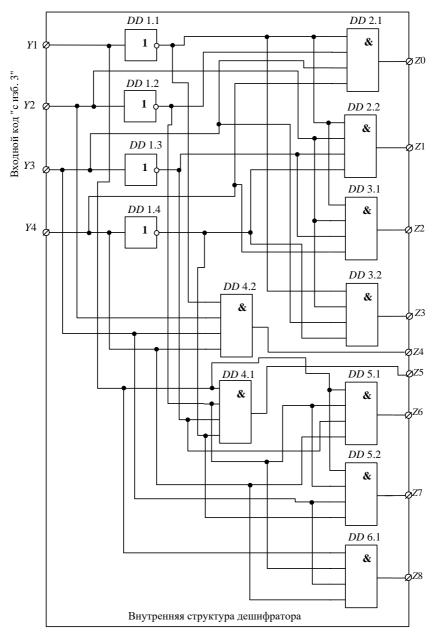

Построим схему дешифратора в базисе «И-ИЛИ-НЕ» по полученным формулам без их упрощения (рисунок 1.5).

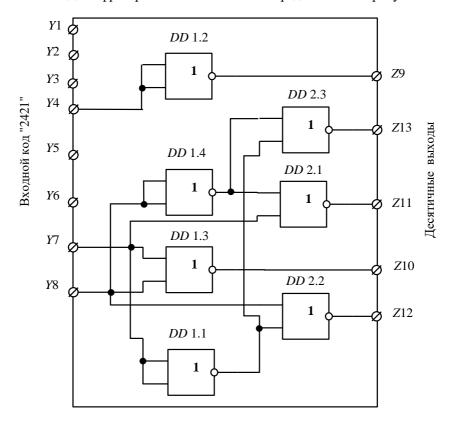

Рассмотрим пример реализации схемы дешифратора, заданного таблицей 1.4, предназначенного для расшифровки чисел кода «2421» от 9 до 13 (в десятичном эквиваленте) в базисе «ИЛИ-НЕ» [1].

|            | Входной код «2421» |            |            |            |            |            |            |       |  |  |

|------------|--------------------|------------|------------|------------|------------|------------|------------|-------|--|--|

|            | дес                | сятки      |            |            | единицы    |            |            | число |  |  |

| <i>Y</i> 1 | <i>Y</i> 2         | <i>Y</i> 3 | <i>Y</i> 4 | <i>Y</i> 5 | <i>Y</i> 6 | <i>Y</i> 7 | <i>Y</i> 8 | Zi    |  |  |

| 0          | 0                  | 0          | 0          | 1          | 1          | 1          | 1          | 9     |  |  |

| 0          | 0                  | 0          | 1          | 0          | 0          | 0          | 0          | 10    |  |  |

| 0          | 0                  | 0          | 1          | 0          | 0          | 0          | 1          | 11    |  |  |

| 0          | 0                  | 0          | 1          | 0          | 0          | 1          | 0          | 12    |  |  |

| 0          | 0                  | 0          | 1          | 0          | 0          | 1          | 1          | 13    |  |  |

Таблица 1.4 – **Таблица истинности дешифратора из кода «2421»**

Так как код «2421» определен для десятичных чисел от 0 до 9, то используем *двоично-десятичный принцип построения кода*. Тогда и дешифратор будет двоично-десятичным.

Запишем формулы связи между входами и выходами и преобразуем их по правилу де Моргана к виду, удобному для реализации в базисе «ИЛИ-НЕ». При записи формул учтем, что разряды Y1, Y2 и Y3 всегда равны нулю в таблице, т. е. являются незначащими. В этом случае их можно исключить из рассмотрения, поскольку по этим разрядам выходные функции не разделяются. Таким образом Z9=

$$= \overline{Y}4 Y5 Y6 Y7 Y8 = \overline{Y}4 \sqrt{\overline{Y}5} \sqrt{\overline{Y}6} \sqrt{\overline{Y}7} \sqrt{\overline{Y}8} = Y4 \downarrow \overline{Y}5 \downarrow \overline{Y}6 \downarrow \overline{Y}7 \downarrow \overline{Y}8;$$

$$Z10 = Y4 \overline{Y}5 \overline{Y}6 \overline{Y}7 \overline{Y}8 = \overline{Y}4 \downarrow Y5 \downarrow Y6 \downarrow Y7 \downarrow Y8; Z11 = \overline{Y}4 \downarrow Y5 \downarrow$$

$$\downarrow Y6 \downarrow Y7 \downarrow \overline{Y}8; Z12 = \overline{Y}4 \downarrow Y5 \downarrow Y6 \downarrow \overline{Y}7 \downarrow Y8; Z13 = \overline{Y}4 \downarrow Y5 \downarrow$$

$$\downarrow Y6 \downarrow \overline{Y}7 \downarrow \overline{Y}8$$

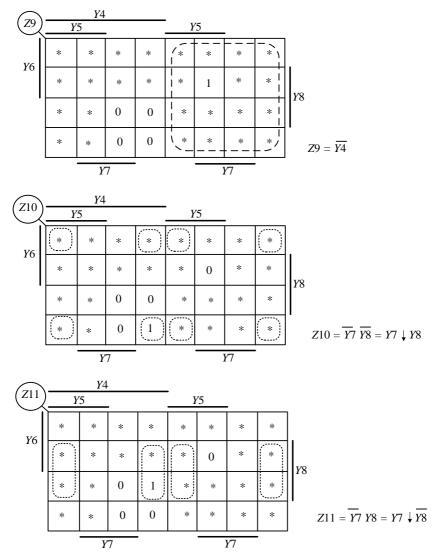

Анализируя данные таблицы 1.4, можно заключить, что она обладает большой избыточностью. Для пяти чисел десятичного кода

используются пять разрядов двоичного кода. В таком случае мы можем упростить выходные функции, используя методику минимизации частично заданных функций на основе карт Карно.

Рисунок 1.5 – Схема дешифратора из кода «с избытком 3»

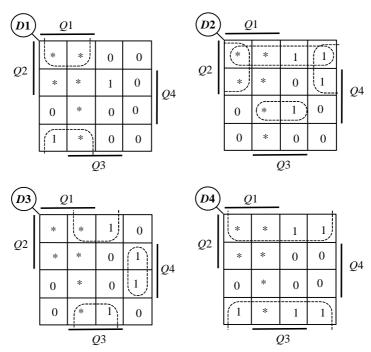

В данном случае существенным является то, что единице может быть равна только одна из задаваемых клеток карты, а остальные должны быть равны нулю. Карты Карно для функций Z9-Z11 представлены на рисунке 1.6.

Рисунок 1.6 – Упрощение функций алгебры логики дешифратора из кода «2421»

По аналогии получим упрощенные выражения для функций Z12 и Z13:  $Z12 = Y7 \overline{Y}8 = \overline{Y}7 \downarrow Y8$ ;  $Z13 = Y7 Y8 = \overline{Y}7 \downarrow \overline{Y}8$ . После упрощения функций видно, что разряды кода Y5 и Y6 также исключены, так как по ним выходные функции не разделяются.

Схема дешифратора в базисе «ИЛИ-НЕ» представлена на рисунке 1.7.

Рисунок 1.7 - Схема дешифратора из кода «2421»

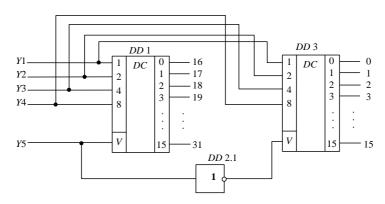

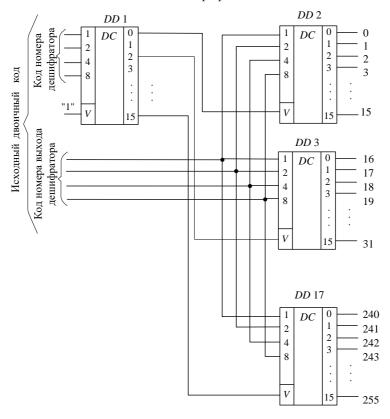

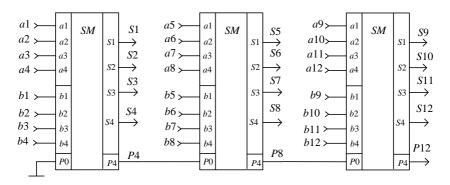

Промышленностью выпускаются дешифраторы с входами разрешения, которые можно использовать для увеличения разрядности обрабатываемых кодов (рисунок 1.8).

Если требуется увеличить значительно количество выходных и входных разрядов, то можно использовать многоступенчатые схемы включения дешифраторов (рисунок 1.9).

Рисунок 1.8 — Схема включения дешифраторов для увеличения количества выходных разрядов

Рисунок 1.9 – Схема двухступенчатого дешифратора

Рассмотрим далее примеры реализации преобразователей кодов и распространенного класса дешифраторов, предназначенного для перевода двоичного кода «8421» в код семисегментного индикатора.

#### 1.3 ПРЕОБРАЗОВАТЕЛИ КОДОВ

**Преобразователь кодов** – комбинационное дискретное устройство, предназначенное для перевода одного двоичного кода в другой двоичный код [1, 3].

Эти дискретные устройства часто применяются в системах автоматики с целью получения из обычных безызбыточных кодов более сложных избыточных кодов. Избыточные коды позволяют только обнаруживать или обнаруживать и исправлять ошибки в кодовых словах при передаче сигналов по линиям связи на большие расстояния.

Существует два способа синтеза преобразователей кодов: с использованием одной таблицы истинности и свойства независимости входов и выходов и путем последовательного включения дешифратора и шифратора [1, 4].

Рассмотрим **примеры построения преобразователей кодов** на основе свойства независимости входов и выходов по одной таблице истинности.

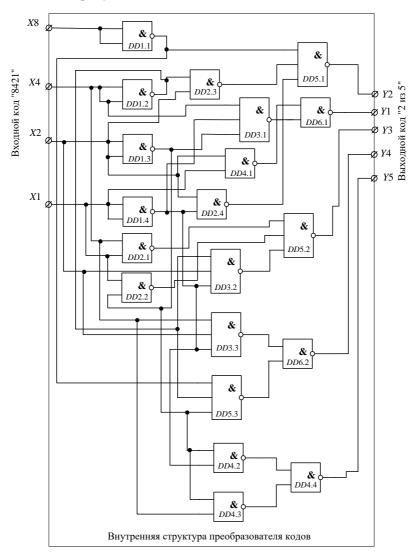

Пусть требуется построить преобразователь кодов для перевода чисел типового кода «8421» в код «2 из 5» в базисе «И-НЕ» для чисел от 0 до 8. Составим таблицу истинности преобразователя (таблица 1.5) в которой отражаются все необходимые комбинации исходного кода «8421» и все соответствующие им комбинации получаемого кода «2 из 5».

Таблица 1.5 — Таблица истинности преобразователя из кода «8421» в кол «2 из 5»

| Десятичное | Ис | ходный і   | код (вход | ы)         |            | Получае    | мый код (  | (выходы)   |            |

|------------|----|------------|-----------|------------|------------|------------|------------|------------|------------|

| число      | X8 | <i>X</i> 4 | X2        | <i>X</i> 1 | <i>Y</i> 5 | <i>Y</i> 4 | <i>Y</i> 3 | <i>Y</i> 2 | <i>Y</i> 1 |

| 0          | 0  | 0          | 0         | 0          | 1          | 1          | 0          | 0          | 0          |

| 1          | 0  | 0          | 0         | 1          | 0          | 1          | 1          | 0          | 0          |

| 2          | 0  | 0          | 1         | 0          | 0          | 0          | 1          | 1          | 0          |

| 3          | 0  | 0          | 1         | 1          | 0          | 0          | 0          | 1          | 1          |

| 4          | 0  | 1          | 0         | 0          | 1          | 0          | 0          | 0          | 1          |

| 5          | 0  | 1          | 0         | 1          | 1          | 0          | 1          | 0          | 0          |

| 6          | 0  | 1          | 1         | 0          | 0          | 1          | 0          | 1          | 0          |

| 7          | 0  | 1          | 1         | 1          | 0          | 0          | 1          | 0          | 1          |

| 8 1 0 | 0 0 1 | 0 0 | 1 ( | ) |

|-------|-------|-----|-----|---|

|-------|-------|-----|-----|---|

Для каждой выходной функции составляется совершенная дизьюнктивная нормальная форма от одних и тех же входных переменных на основе свойства независимости выходов:  $Y5 = \overline{X}8\overline{X}4\overline{X}2\overline{X}1 \lor \overline{X}8X4\overline{X}2\overline{X}1 \lor$

$\sqrt{X}8X4\overline{X}2X1 \vee X8\overline{X}4\overline{X}2\overline{X}1; Y4 = \overline{X}8\overline{X}4\overline{X}2\overline{X}1 \vee \overline{X}8\overline{X}4\overline{X}2X1 \vee \overline{X}8X4X2\overline{X}1; Y3 = \overline{X}8\overline{X}4\overline{X}2X1 \vee \overline{X}8\overline{X}4X2\overline{X}1 \vee \overline{X}8X4X2\overline{X}1 \vee \overline{X}8X4\overline{X}2\overline{X}1 \vee \overline{X}8\overline{X}4\overline{X}2\overline{X}1 \vee \overline{X}1 \vee \overline{X}8\overline{X}4\overline{X}2\overline{X}1 \vee \overline{X}8\overline{X}4\overline{X$

Затем полученные функции выходов упрощаются одним из известных методов минимизации. Упростим функцию Y5 методом Квайна — Мак-Класки. Для этого перепишем ее, заменив переменные их значениями ( $\overline{X}i=0$ , а Xi=1). Тогда  $Y5=0000\lor0100\lor0101\lor1000$ . Кроме того, учтем, что функция Y5 является частично заданной, в которой кодовые комбинации для чисел 9-15 не используются (поскольку с использованием четырех переменных реализуются  $2^4=16$  кодовых слов), поэтому при упрощении данной и всех остальных функций в этом случае необходимо применить методику упрощения частично заданных функций [5].

Доопределим функцию Y5, добавив в нее кодовые комбинации чисел 9–15, и получим функцию  $Y_5^1 = 0000 \lor 0100 \lor 0101 \lor 1000 \lor \lor 1001 \lor 1010 \lor \lor 1011 \lor 1100 \lor 1101 \lor 1110 \lor 1111$ .

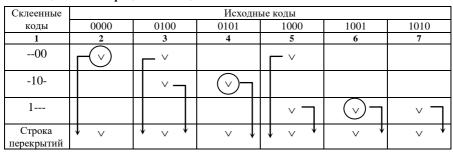

Разобьем полученные кодовые слова функции по группам в зависимости от числа единиц в них (таблица 1.6). Применим *операцию склеивания* к кодам соседних по номерам групп [1, 5]. Склеиванию подвержены лишь те коды, которые различаются одним из четырех символов на соответствующей позиции. После склеивания на месте склеивания символа проставляется знак прочерк «-», и код перемещается в группу с меньшим номером.

После первой операции склеивания процесс повторяется для тех склеенных кодов, у которых прочерки находятся на одинаковых позициях. После второй итерации склеивания процесс опять повторяется.

Когда операцию склеивания больше применить нельзя, переходим к *операции поглощения*. Для этого составляем таблицу поглощений (таблица 1.7). В столбцах данной таблицы размещаются все исходные коды, а в строках — коды, оставшиеся после склеивания. В клетках

таблицы на пересечении соответствующих строки и столбца проставляются отметки, если совпадают символы строки и столбца на позициях, где нет прочерков.

Таблица 1.6 – Операции склеивания

| Номер<br>группы | Исходные коды групп    | Коды после первого склеивания            |

|-----------------|------------------------|------------------------------------------|

| 1               | 2                      | 3                                        |

| 0               | 0000                   | 0-00, -000                               |

| 1               | 0100, 1000             | 010-, -100, 100-, 10-0, 1-00             |

| 2               | 0101, 1001, 1010, 1100 | -101, 10-1, 1-01, 101-, 1-10, 110-, 11-0 |

| 3               | 1011, 1101, 1110       | 1-11, 11-1, 111-                         |

| 4               | 1111                   |                                          |

#### Продолжение таблицы 1.6

| Номер<br>группы | Коды после второго склеивания | Коды после третьего склеивания |

|-----------------|-------------------------------|--------------------------------|

| 1               | 4                             | 5                              |

| 0               | 00                            | 00                             |

| 1               | -10-, 10, 1-0-, 10            | -10-, 1                        |

| 2               | 11, 1-1-, 11                  |                                |

| 3               |                               |                                |

| 4               |                               |                                |

#### Таблица 1.7 – Операции поглощения

#### Продолжение таблицы 1.7

| Склеенные            |      | Исходные коды        |            |           |      |  |

|----------------------|------|----------------------|------------|-----------|------|--|

| коды                 | 1011 | 1100                 | 1101       | 1110      | 1111 |  |

| 1                    | 8    | 9                    | 10         | 11        | 12   |  |

| 00                   |      | <b></b>              |            |           |      |  |

| -10-                 |      |                      |            |           |      |  |

| 1                    | · ¬  |                      | · ¬        | · ¬       | · ¬  |  |

| Строка<br>перекрытий | √    | <b>11</b> \( \tau \) | <b>1</b> V | · · · · · | V    |  |

В строке перекрытий таблицы 1.7 все клетки должны быть заполнены отметками, снесенными от склеенных кодов (перенос отметок в строку перекрытий в таблице показан стрелками). В первую очередь в строку перекрытий сносятся отметки ядер функции, т.е. тех склеенных кодов, для которых хотя бы в одном столбце есть отметка только от данного склеенного кода. В рассматриваемой таблице все склеенные коды будут ядрами. Поэтому упрощенная функция будет иметь следующий вид  $Y_{\rm 5\,min}^1 = --00 \lor -10 - \lor 1---$ .

Поскольку функция задана частично, необходимо проверить ее также на возможность перекрытий с функцией *Y5* (таблица 1.8).

Работая над данными таблицы, выясняем, что для перекрытия исходной функции достаточно лишь двух из трех склеенных кодов —00 и -10—. Тогда окончательный результат упрощения функции запишем как  $Y_5^{\min} = -0.00 \lor -10$ —. Заменим невычеркнутые значения переменными и получим упрощенную функцию  $Y_5 = \overline{X} \, 2 \, \overline{X} \, 1 \lor X \, 4 \, \overline{X} \, 2$ .

${

m T}$ аблица 1.8 —  ${

m Перекрытие}$  функций  ${

m Y}5$  и  ${

m Y}_{

m 5min}^1$

| v <sup>1</sup>       |      | ,         | Y5    |         |

|----------------------|------|-----------|-------|---------|

| <sup>1</sup> 5min    | 0000 | 0100      | 0101  | 1000    |

| 00                   | V    | \ \ \ \   |       | \ \ \ \ |

| -10-                 |      | L ^       |       |         |

| 1                    |      |           |       | V       |

| Строка<br>перекрытий | V    | \ \ \ \ \ | \ \ \ | V       |

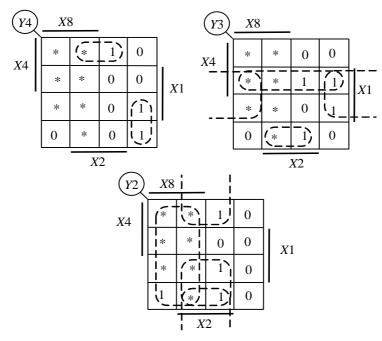

Функции Y4, Y3 и Y2 упростим с помощью *карт Карно* (рисунок 1.10), а функцию Y1- *методом существенных переменных*. В результате упрощения на основе карт Карно получим следующие функции:  $Y2=X8\vee\overline{X}4X2\vee X2\overline{X}1,Y3=X4X1\vee\overline{X}2X1\vee\overline{X}4X2\overline{X}1,$   $Y4=X4X2\overline{X}1\vee\overline{X}8\overline{X}4\overline{X}2$ .

Для минимизации функции Y1 составим таблицу существенных переменных (таблица 1.9) в столбцах которой будут запрещенные (где которых Y1=0), а в строках — разрешенные (где Y1=1) наборы переменных [1,5].

Заполним таблицу 1.9 путем поочередного сравнения разрешенных наборов каждой строки со всеми запрещенными

наборами. В клетках на пересечении разрешенных и запрещенных наборов записываем несовпадающие элементы в таком виде, как они представлены в разрешенном наборе. Затем в таблице определяем клетки, содержащие по одной переменной. Эти переменные обводим кружком и записываем в столбец остатков. Если переменных несколько, в столбец остатков их записываем через знак умножения.

Рисунок 1.10 – Упрощение функций У2, У3 и У4 с помощью карт Карно

Далее отмечаем знаком «

» те члены строки, в которые входят обведенные кружком переменные, и их исключаем из дальнейшего рассмотрения.

Так как в таблице 1.9 оказались отмечены знаком «

» все клетки, в которых переменная не обведена кружком, то далее составляем таблицу покрытий существенных переменных (таблица 1.10). В строках таблицы размещаем остатки, а в столбцах — разрешенные наборы.

Обрабатываем таблицу по аналогии с таблицей покрытий в методе Квайна — Мак-Класки. Результат минимизации функции Y1 методом существенных переменных будет следующим:  $Y1 = X2X1 \lor$

#### $\vee X4\overline{X}2\overline{X}1.$

Таблица 1.9 – Таблица существенных переменных

| Разрешенные                                 |                                                        | Запрещенн                                   | ые наборы                                   |                                  |

|---------------------------------------------|--------------------------------------------------------|---------------------------------------------|---------------------------------------------|----------------------------------|

| наборы                                      | $\overline{X}8\overline{X}4\overline{X}2\overline{X}1$ | $\overline{X}8\overline{X}4\overline{X}2X1$ | $\overline{X}8\overline{X}4X2\overline{X}1$ | $\overline{X}8X4\overline{X}2X1$ |

| 1                                           | 2                                                      | 3                                           | 4                                           | 5                                |

| $\overline{X}8\overline{X}4X2X1$            | X2X1 V                                                 | X2)                                         | (X1)                                        | $\overline{X}4X2 \vee$           |

| $\overline{X}8X4\overline{X}2\overline{X}1$ | X4                                                     | $X4\overline{X}1 \vee$                      | $X4\overline{X}2 V$                         | $\overline{X1}$                  |

| $\overline{X}8X4X2X1$                       | X4X2X1 V                                               | X4X2 V                                      | X4X1 V                                      | X2                               |

#### Продолжение таблицы 1.9

| Разрешенные                                 | Запрещенн                        | Запрещенные наборы                          |                                |  |

|---------------------------------------------|----------------------------------|---------------------------------------------|--------------------------------|--|

| наборы                                      | $\overline{X}8X4X2\overline{X}1$ | $X8\overline{X}4\overline{X}2\overline{X}1$ | Остатки                        |  |

| 1                                           | 6                                | 7                                           | 8                              |  |

| $\overline{X}8\overline{X}4X2X1$            | $\overline{X}4X1 \vee$           | $\overline{X}8X2X1 \lor$                    | X1X2                           |  |

| $\overline{X}8X4\overline{X}2\overline{X}1$ | $\overline{\overline{X}}$ 2      | $\overline{X}8X4 \vee$                      | $X4\overline{X}1\overline{X}2$ |  |

| $\overline{X}8X4X2X1$                       | XI                               |                                             | X2X1                           |  |

Таблица 1.10 – Покрытие существенных переменных

| Остатки                        | Существенные переменные (разрешенные наборы) |                                             |                       |  |  |

|--------------------------------|----------------------------------------------|---------------------------------------------|-----------------------|--|--|

|                                | $\overline{X}8\overline{X}4X2X1$             | $\overline{X}8X4\overline{X}2\overline{X}1$ | $\overline{X}8X4X2X1$ |  |  |

| X1X2                           | V                                            |                                             | V                     |  |  |

| $X4\overline{X}1\overline{X}2$ |                                              | V                                           |                       |  |  |

Преобразуем полученные функции к виду, удобному для представления в базисе «И-НЕ» по правилу де Моргана [5]:

$$Y1 = \overline{\overline{X2X1}} \ \overline{X4\overline{X}2\overline{X1}} = (X2 \mid X1) \mid (X4 \mid \overline{X}2 \mid \overline{X}1);$$

$$Y2 = \overline{\overline{X8}} \ \overline{\overline{\overline{X4X2}}} \ \overline{\overline{X2X1}} = \overline{X8} \mid (\overline{X}4 \mid X2) \mid (X2 \mid \overline{X}1);$$

$$Y3 = \overline{\overline{X4X1}} \ \overline{\overline{\overline{X2X1}}} \ \overline{\overline{\overline{X4X2X1}}} = (X4 \mid X1) \mid (\overline{X2} \mid X1) \mid (\overline{X4} \mid X2 \mid \overline{X}1);$$

$$Y4 = (X4 \mid X2 \mid \overline{X1}) \mid (\overline{X8} \mid \overline{X4} \mid \overline{X2}); \ Y5 = (\overline{X2} \mid \overline{X1}) \mid (X4 \mid \overline{X2}).$$

Теперь можно построить схему преобразователя кодов на общих входах (рисунок 1.11).

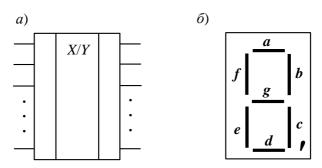

Преобразователь кодов имеет условное графическое обозначение,

#### показанное на рисунке 1.12, а.

Рисунок 1.11 – Схема преобразователя из кода «8421» в код «2 из 5»

Рассмотрим пример построения преобразователя кодов для вывода двоичных чисел на семисегментный индикатор (рисунок  $1.12, \delta$ ). Если свечение сегмента индикатора отождествлять с

логической единицей на выходе преобразователя кодов, то в таком случае таблица истинности преобразователя для чисел от 0 до 9 в десятичном эквиваленте будет иметь вид, представленный в таблице 1.11.

Рисунок 1.12 — Условные обозначения преобразователя кодов (a) и семисегментного индикатора ( $\delta$ )

Таблица 1.11 — Таблица истинности преобразователя в код семисегментного индикатора

| Десяти        | есяти Входной код «8421» Выходной код (состояния сегментов индикатор |            |            |            |   |   | гора) |   |   |   |   |

|---------------|----------------------------------------------------------------------|------------|------------|------------|---|---|-------|---|---|---|---|

| чное<br>число | X8                                                                   | <i>X</i> 4 | <i>X</i> 2 | <i>X</i> 1 | а | b | c     | d | e | f | g |

| 0             | 0                                                                    | 0          | 0          | 0          | 1 | 1 | 1     | 1 | 1 | 1 | 0 |

| 1             | 0                                                                    | 0          | 0          | 1          | 0 | 1 | 1     | 0 | 0 | 0 | 0 |

| 2             | 0                                                                    | 0          | 1          | 0          | 1 | 1 | 0     | 1 | 1 | 0 | 1 |

| 3             | 0                                                                    | 0          | 1          | 1          | 1 | 1 | 1     | 1 | 0 | 0 | 1 |

| 4             | 0                                                                    | 1          | 0          | 0          | 0 | 1 | 1     | 0 | 0 | 1 | 1 |

| 5             | 0                                                                    | 1          | 0          | 1          | 1 | 0 | 1     | 1 | 0 | 1 | 1 |

| 6             | 0                                                                    | 1          | 1          | 0          | 1 | 0 | 1     | 1 | 1 | 1 | 1 |

| 7             | 0                                                                    | 1          | 1          | 1          | 1 | 1 | 1     | 0 | 0 | 0 | 0 |

| 8             | 1                                                                    | 0          | 0          | 0          | 1 | 1 | 1     | 1 | 1 | 1 | 1 |

| 9             | 1                                                                    | 0          | 0          | 1          | 1 | 1 | 1     | 1 | 0 | 1 | 1 |

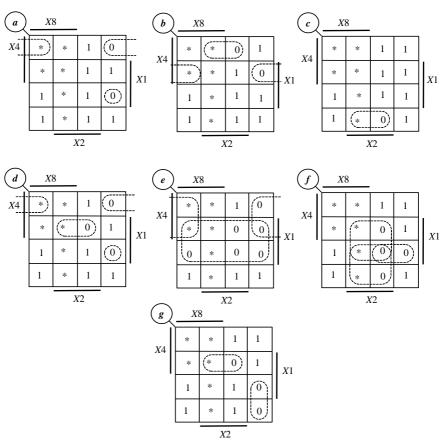

Упростим выходные частично заданные функции с помощью карт Карно (рисунок 1.13) и построим схему преобразователя в базисе «ИЛИ-НЕ».

В результате упрощения на основе карт Карно получим следующие выражения:

$$a = (\overline{X}4 \lor X2 \lor X1)(X8 \lor X4 \lor X2 \lor \overline{X}1), \ b = (\overline{X}4 \lor \lor \overline{X}2 \lor X1)(\overline{X}4 \lor X2 \lor \overline{X}1), \ c = X4 \lor \overline{X}2 \lor X1, \ d = (\overline{X}4 \lor X2 \lor X1) \times \overline{X}2 \lor X1$$

$\times (\overline{X}4 \vee \overline{X}2 \vee \overline{X}1)(X8 \vee X4 \vee X2 \vee \overline{X}1) , \ e = \overline{X}1(\overline{X}4 \vee X2) , \ f = (\overline{X}1 \vee \overline{X}2)(X4 \vee \overline{X}2)(X8 \vee X4 \vee \overline{X}1) , \ g = (\overline{X}4 \vee \overline{X}2 \vee \overline{X}1)(X8 \vee X4 \vee X2) .$

Рисунок 1.13 – Упрощение функций преобразователя в семисегментный код

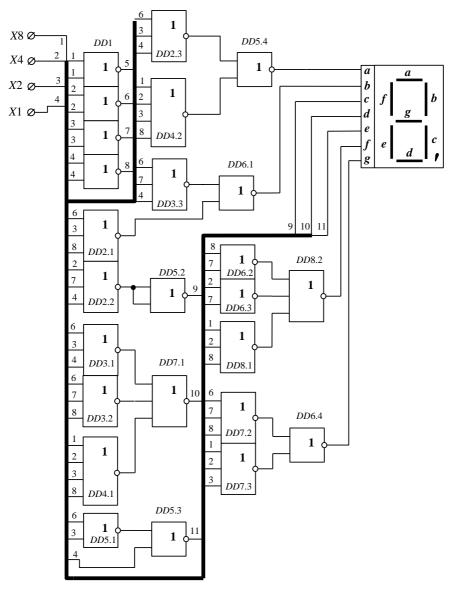

Преобразуем полученные функции к виду, удобному для построения в базисе «ИЛИ-НЕ»:

$d = (\overline{X}4 \downarrow X2 \downarrow X1) \downarrow (\overline{X}4 \downarrow \overline{X}2 \downarrow \overline{X}1) \downarrow (X8 \downarrow X4 \downarrow X2 \downarrow \overline{X}1),$   $f = (\overline{X}1 \downarrow \overline{X}2) \downarrow (X4 \downarrow \overline{X}2) \downarrow (X8 \downarrow X4 \downarrow \overline{X}1), \ g = (\overline{X}4 \downarrow \overline{X}2 \downarrow \overline{X}1) \downarrow$   $\downarrow (X8 \downarrow X4 \downarrow X2).$

Построим схему преобразователя из кода «8421» в семисегментный код (рисунок 1.14) на базе общей шины.

Рисунок 1.14 — Схема преобразователя из кода «8421» в семисегментный код и ее подключение

Далее рассмотрим процесс синтеза коммутирующих комбинационных устройств – мультиплексоров.

#### 1.4 МУЛЬТИПЛЕКСОРЫ

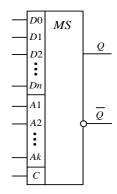

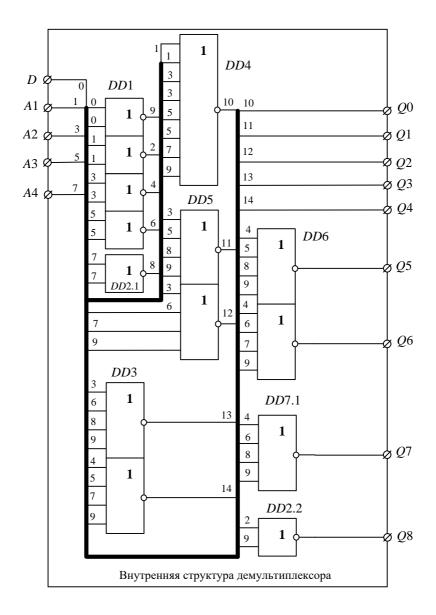

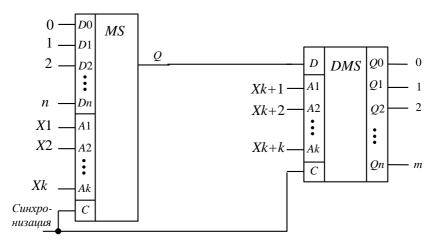

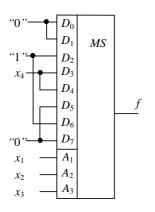

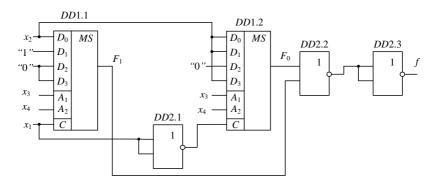

**Мультиплексор** — комбинационное дискретное устройство, имеющее в общем случае входы данных Dn, адресные входы Ak, вход синхронизации C и выход Q [1]. Количество входов данных и адресных входов связано соотношением  $n \le 2^k - 1$  (рисунок 1.15).

В процессе функционирования мультиплексор подключает к выходу Q один из множества входов данных, номер которого задан на адресных входах при наличии сигнала синхронизации, который выступает в роли сигнала разрешения коммутации информации мультиплексором.

Вход синхронизации может отсутствовать, тогда мультиплексор будет асинхронным.

В устройствах и системах автоматики, телемеханики и связи мультиплексоры находят широкое применение не только в

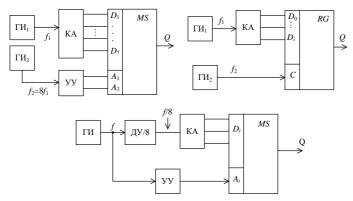

Рисунок 1.15 – Условное обозначение мультиплексора

качестве устройств коммутации информации с нескольких входов на один выход, но также совместно со счетчиками импульсов их применяют для преобразования данных из параллельной формы представления в последовательную форму (в так называемых распределителях). Преобразователи формы применяются в системах распределительной телемеханики кодовой И селекцией (избиранием объектов). Также мультиплексоры являются компонентами цифровых систем передачи информации.

Для построения мультиплексора необходимо составить его таблицу истинности, по которой получаем выражение функции выхода мультиплексора в зависимости от множеств входных сигналов A,D и C.

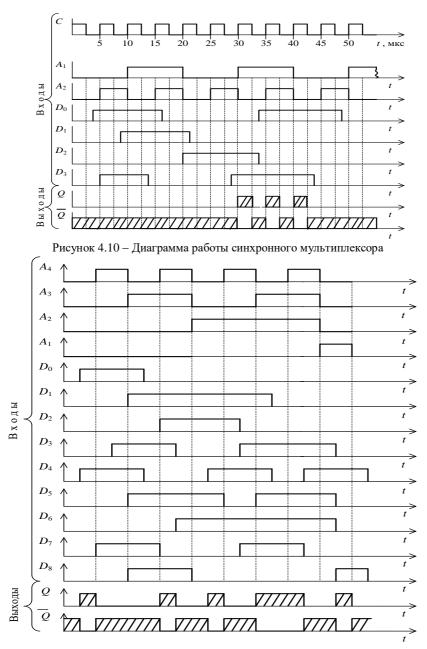

Пусть требуется получить схему синхронного мультиплексора на четыре входа данных в базисе «И-ИЛИ-НЕ». В этом случае необходимы два адресных входа, а таблица истинности мультиплексора имеет следующий вид (таблица 1.12):

Таблица 1.12 – Таблица истинности синхронного мультиплексора на 4 входа ланных

| Адресн | ые входы | Вход синхронизации | Выход |

|--------|----------|--------------------|-------|

| A1     | A1 A2    |                    | Q     |

| 0 | 0 | 1 | D0         |

|---|---|---|------------|

| 0 | 1 | 1 | <i>D</i> 1 |

| 1 | 0 | 1 | D2         |

| 1 | 1 | 1 | D3         |

| * | * | 0 | 0          |

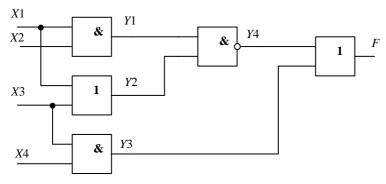

Получим выражение функции выхода в виде совершенной дизъюнктивной нормальной формы  $Q = \overline{A}1\overline{A}2CD0 \lor \overline{A}1A2CD1 \lor A1\overline{A}2CD2 \lor A1A2CD3 = C(\overline{A}1\overline{A}2D0 \lor \overline{A}1A2D1 \lor A1\overline{A}2D2 \lor A1A2D3)$ .

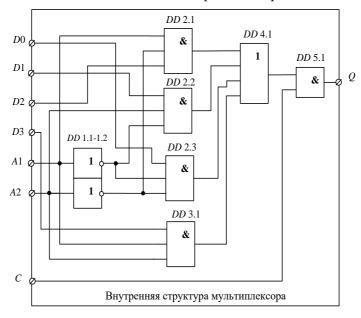

На основе формулы построим схему мультиплексора (рисунок 1.16).

Рассмотрим процесс синтеза асинхронного мультиплексора на девять входов данных в базисе «И-НЕ». Асинхронный мультиплексор не имеет входа синхронизации и поэтому его используют в медленнодействующих схемах. Его функционирование определяется таблицей 1.13. Количество адресных входов из соотношения  $n \le 2^k - 1$  или  $9 \le 2^4 - 1$  равно четырем.

Рисунок 1.16 – Схема синхронного мультиплексора на четыре входа данных

Таблица 1.13 – Таблица истинности асинхронного мультиплексора на 9 входов данных

| Адресные входы | Выход |

|----------------|-------|

| A1 | A2 | A3 | A4 | Q          |

|----|----|----|----|------------|

| 0  | 0  | 0  | 0  | D0         |

| 0  | 0  | 0  | 1  | <i>D</i> 1 |

| 0  | 0  | 1  | 0  | D2         |

| 0  | 0  | 1  | 1  | D3         |

| 0  | 1  | 0  | 0  | D4         |

| 0  | 1  | 0  | 1  | D5         |

| 0  | 1  | 1  | 0  | D6         |

| 0  | 1  | 1  | 1  | D7         |

| 1  | 0  | 0  | 0  | D8         |

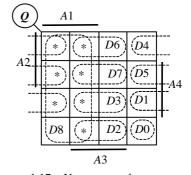

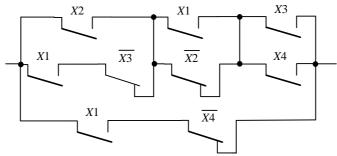

Поскольку не все комбинации адресных входов задействованы для синтеза мультиплексора, то выходная функция задана частично и мы можем ее упростить с помощью карты Карно (рисунок 1.17). В карте будет столько контуров, сколько входов данных у синтезируемого мультиплексора. Звездочками в карте отмечены незадействованные комбинации адресных входов.

В результате обработки карты Карно получаем функцию выхода мультиплексора  $Q = \overline{A}1\overline{A}2\overline{A}3\overline{A}4\ D0\lor \\ \lor \overline{A}2\overline{A}3A4\ D1\lor \overline{A}2A3\overline{A}4\ D2\lor \\ \lor \overline{A}2\overline{A}3A4D3\lor A2\overline{A}3\overline{A}4D4\lor \\ \lor A2\overline{A}3A4D5\lor A2A3\overline{A}4D6 \\ \lor A2A3A4D7\lor A1D8 \, .$

Рисунок 1.17 – Упрощение функции выхода мультиплексора на девять входов данных

С помощью закона <sub>Рисунок</sub> двойственности преобразуем <sub>мультип</sub> полученную функцию к виду, удобному для построения в базисе «И-НЕ»:

$$Q = (\overline{A}1 | \overline{A}2 | \overline{A}3 | \overline{A}4 | D0) | (\overline{A}2 | \overline{A}3 | A4 | D1) | (\overline{A}2 | A3 | \overline{A}4 | D2) |$$

$$| (\overline{A}2 | A3 | A4 | D3) | (A2 | \overline{A}3 | \overline{A}4 | D4) | (A2 | \overline{A}3 | A4 | D5) | (A2 | A3 | A4 | D7) | (A1 | D8).$$

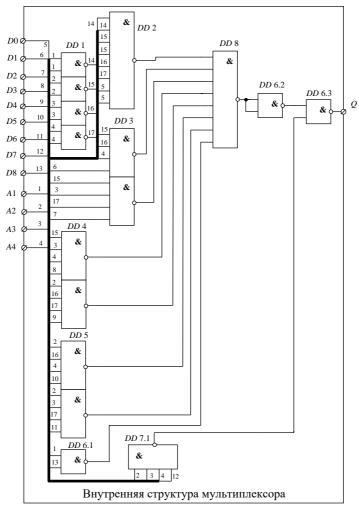

На основе полученной формулы построим схему мультиплексора (рисунок 1.18) с использованием шинной структуры.

На схеме у элемента *DD*2 использованы только пять входов из восьми, поэтому неиспользуемые входы подключены параллельно к используемым входам (ножки 14, 15 и 5). По формуле выхода мультиплексора необходимо реализовать функцию Шеффера на 9

входов. Данная функция реализована на элементах DD8, DD6.2 и DD6.3, так как отсутствует микросхема на девять входов. При этом выполнено преобразование исходной функции по принципу

$F = \overline{X1X2X3X4X5X6X7X8X9} = \overline{X1X2X3X4X5X6X7X8X9} = (\overline{X1|X2|X3|X4|X5|X6|X7|X8}) | X9.$

Рисунок 1.18 – Схема асинхронного мультиплексора на 9 входов данных

Рассмотрим далее процесс построения демультиплексоров -

устройств, выполняющих обратную мультиплексорам задачу.

#### 1.5 ДЕМУЛЬТИПЛЕКСОРЫ

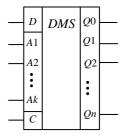

**Демультиплексор** — комбинационное дискретное устройство, имеющее в общем случае вход данных D, адресные входы Ak, вход синхронизации C и выходы Qn [4]. Количество выходов и адресных входов связано соотношением  $n \le 2^k - 1$  (рисунок 1.19).

В процессе функционирования демультиплексор подключает вход данных к тому из выходов, номер которого задан на адресных входах при наличии сигнала синхронизации. Демультиплексоры также бывают и асинхронными. В таком

случае у них отсутствует вход C.

В системах и устройствах автоматики, телемеханики и связи демультиплексоры широко используют не только в качестве устройств коммутации с одного входа на несколько выходов, но также совместно со счетчиками импульсов ИΧ применяют для преобразования данных ИЗ последовательной формы

Рисунок 1.19 – Условное обозначение демультиплексора

представления в параллельную. Как правило, такое преобразование выполняется на приемной стороне систем телемеханики и связи.

При построении демультиплексора составляют его таблицу истинности, по которой получают выражения функций выходов демульти-плексора в зависимости от множества входных сигналов  $A,\,D$  и C.

Пусть необходимо построить схему синхронного демультиплексора на пять выходов данных в базисе «И-НЕ». В этом случае необходимы три адресных входа, а функционирование демультиплексора определяется в соответствии с таблицей 1.14.

Поскольку при трех адресных входах можно коммутировать данные на восемь выходов по формуле  $n=2^k$ , а в данном случае используется лишь пять выходов, то их функции будут частично заданы и мы упростим их с помощью карт Карно (рисунок 1.20).

| 1 4 0 3 | таолица 1.14 таолица истипости демультиваемсора на 3 выходов данных |    |    |   |                |        |   |   |   |  |

|---------|---------------------------------------------------------------------|----|----|---|----------------|--------|---|---|---|--|

|         | Входы                                                               |    |    |   |                | Выходы |   |   |   |  |

| A1      |                                                                     | A2 | A3 | С | Q0 Q1 Q2 Q3 Q4 |        |   |   |   |  |

| 0       |                                                                     | 0  | 0  | 1 | D              | 0      | 0 | 0 | 0 |  |

| 0       |                                                                     | 0  | 1  | 1 | 0              | D      | 0 | 0 | 0 |  |

| 0       |                                                                     | 1  | 0  | 1 | 0              | 0      | D | 0 | 0 |  |

| 0       |                                                                     | 1  | 1  | 1 | 0              | 0      | 0 | D | 0 |  |

0

0

0

D

0

0

Таблица 1.14 – Таблица истинности демультиплексора на 5 выходов данных

Рисунок 1.20 – Упрощение функций выходов демультиплексора

Неопределенные состояния в картах  $A1\overline{A}2A3$ ,  $A1A2\overline{A}3$  и A1A2A3. Конъюнкция для выхода Q0 не упрощается, а для остальных выходов получаем следующие выражения:  $Q1 = \overline{A}2A3D$ ,  $Q2 = A2\overline{A}3D$ , Q3 = A2A3D, Q4 = A1D. Тогда выходные функции с учетом входа синхронизации будут иметь следующий вид:  $Q0 = \overline{A}1\overline{A}2\overline{A}3CD$ ;  $Q1 = \overline{A}2A3CD$ ,  $Q2 = A2\overline{A}3CD$ , Q3 = A2A3CD, Q4 = A1CD. Преобразуем полученные функции к виду, удобному для построения в базисе «И-НЕ», с помощью закона двойного отрицания  $Q0 = \overline{\overline{A}1\overline{A}2\overline{A}3CD} = \overline{\overline{A}1|\overline{A}2|\overline{A}3|C|D}$ ,  $Q1 = \overline{\overline{A}2A3CD} = \overline{\overline{A}2|A3|C|D}$ ,  $Q2 = \overline{A2|\overline{A}3|C|D}$ ,  $Q3 = \overline{A2|A3|C|D}$ ,  $Q4 = \overline{A1|C|D}$ .

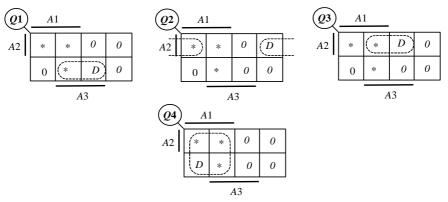

Построим схему демультиплексора (рисунок 1.21).

Рассмотрим процесс синтеза асинхронного демультиплексора на девять выходов данных в базисе «ИЛИ-НЕ», представленного таблицей 1.15.

Рисунок 1.21 — Схема синхронного демультиплексора на 5 выходов данных в базисе «И-НЕ»

Таблица 1.15 – Таблица истинности асинхронного демультиплексора на 9 выходов данных

|    | Bx | оды |    |    |    |    | ]          | Выходы | [  |    |    |    |

|----|----|-----|----|----|----|----|------------|--------|----|----|----|----|

| A1 | A2 | A3  | A4 | Q0 | Q1 | Q2 | <i>Q</i> 3 | Q4     | Q5 | Q6 | Q7 | Q8 |

| 0  | 0  | 0   | 0  | D  | 0  | 0  | 0          | 0      | 0  | 0  | 0  | 0  |

| 0  | 0  | 0   | 1  | 0  | D  | 0  | 0          | 0      | 0  | 0  | 0  | 0  |

| 0  | 0  | 1   | 0  | 0  | 0  | D  | 0          | 0      | 0  | 0  | 0  | 0  |

| 0  | 0  | 1   | 1  | 0  | 0  | 0  | D          | 0      | 0  | 0  | 0  | 0  |

| 0  | 1  | 0   | 0  | 0  | 0  | 0  | 0          | D      | 0  | 0  | 0  | 0  |

| 0  | 1  | 0   | 1  | 0  | 0  | 0  | 0          | 0      | D  | 0  | 0  | 0  |

| 0  | 1  | 1   | 0  | 0  | 0  | 0  | 0          | 0      | 0  | D  | 0  | 0  |

| 0  | 1  | 1   | 1  | 0  | 0  | 0  | 0          | 0      | 0  | 0  | D  | 0  |

| 1  | 0  | 0   | 0  | 0  | 0  | 0  | 0          | 0      | 0  | 0  | 0  | D  |

Поскольку в таблице истинности задействованы не шестнадцать, а девять кодовых слов при четырех адресных переменных, выходные функции будут частично заданы и большинство из них упростятся. Упрощение функций аналогично тому, как это выполнено при построении демультиплексора на пять выходов данных. Только в данном случае используются карты Карно на 16 клеток (так как есть четыре адресных входа). Запишем функции выходов (с учетом упрощения) и преобразуем их к виду, удобному для построения в базисе «ИЛИ-НЕ» с применением закона двойственности:  $Q0 = \overline{A}1\overline{A}2\overline{A}3\overline{A}4D = \overline{A}1 \lor A2 \lor A3 \lor A4 \lor \overline{D} = A1 \downarrow A2 \downarrow A3 \downarrow A4 \downarrow \overline{D} ,$

$$Q0 = A1A2A3A4D = A1 \lor A2 \lor A3 \lor A4 \lor D = A1 \lor A2 \lor A3 \lor A4 \lor D,$$

$$Q1 = \overline{A}2\overline{A}3A4D = A2 \lor A3 \lor \overline{A}4 \lor \overline{D}, Q2 = \overline{A}2A3\overline{A}4D = A2 \lor \overline{A}3 \lor A4 \lor \overline{D},$$

$$Q3 = A2 \lor \overline{A}3 \lor \overline{A}4 \lor \overline{D}, Q4 = \overline{A}2 \lor A3 \lor A4 \lor \overline{D}, Q5 = \overline{A}2 \lor A3 \lor \overline{A}4 \lor \overline{D},$$

$$Q6 = \overline{A}2 \lor \overline{A}3 \lor A4 \lor \overline{D}, Q7 = \overline{A}2 \lor \overline{A}3 \lor \overline{A}4 \lor \overline{D}, Q8 = \overline{A}1 \lor \overline{D}.$$

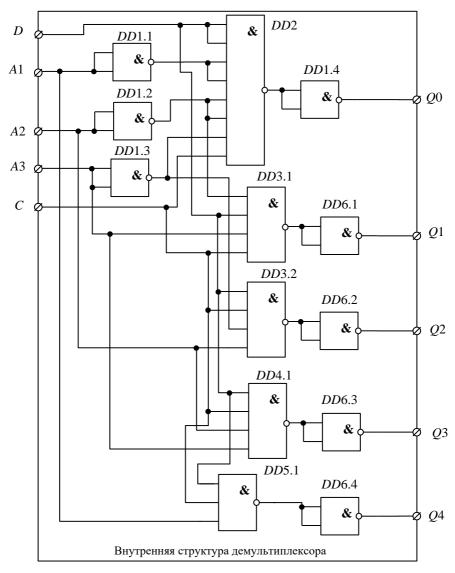

По полученным формулам построим схему мультиплексора с (рисунок использованием обшей шины 1.22). Соединяя мультиплексора последовательно И вход выход данных можно получить устройство, позволяющее демультиплексора, коммутировать любой из входов данных к любому из выходов многоканальный селектор (рисунок 1.23).

Многоканальные селекторы часто используются в цифровых автоматических телефонных станциях для соединения различных абонентов друг с другом.

Рисунок 1.22 — Схема асинхронного демультиплексора на девять выходов данных в базисе «ИЛИ-НЕ»

Рисунок 1.23 – Схема многоканального синхронного селектора

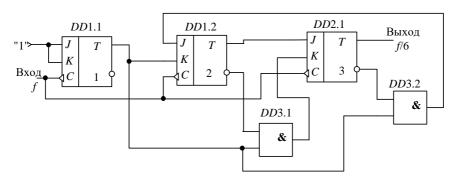

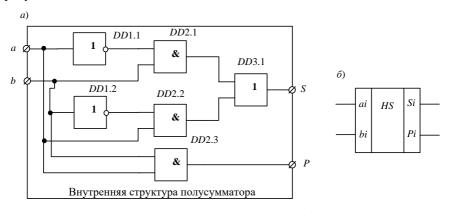

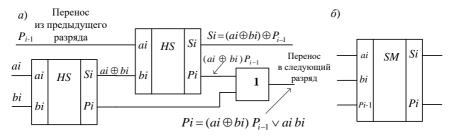

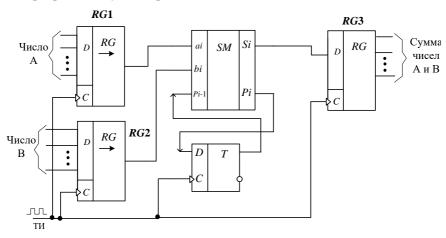

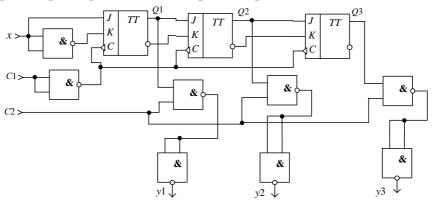

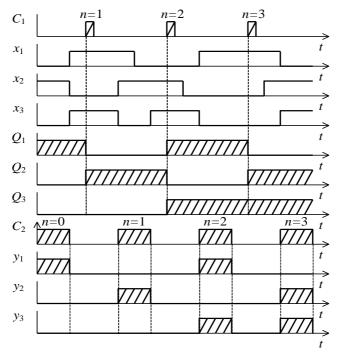

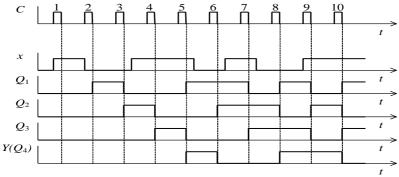

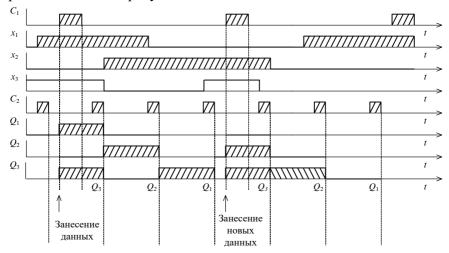

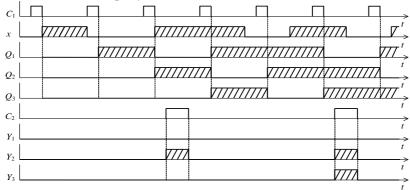

## 1.6 СЧЕТЧИКИ ИМПУЛЬСОВ

**Счетчики импульсов** — это дискретные устройства с памятью, осуществляющие подсчет числа поступающих входных импульсов и хранящих подсчитанное число в виде двоичного кода [3, 6, 7].

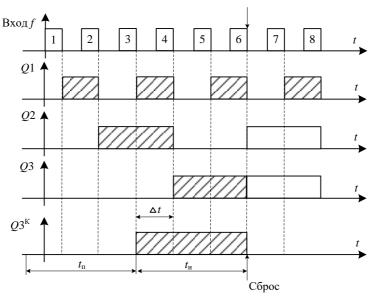

Счетчики характеризуются такими параметрами, как быстродействие и информационная емкость. Быстродействие с счетчика определяется разрешающей способностью  $t_{\rm p}$  и временем установки  $t_{\rm v}$  очередного состояния.

Разрешающая способность обратно пропорциональна частоте входных сигналов ( $t_p = 1/f_{\rm BX}$ ). Поэтому под разрешающей способностью счетчика понимают минимально допустимый интервал времени между двумя входными сигналами, при котором не происходит потеря информации.

*Время установки* счетчика есть промежуток времени от момента поступления входного сигнала до момента завершения переключения счетчика в новое состояние.

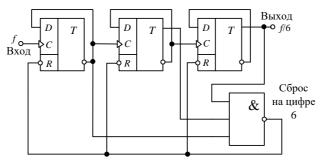

Информационная емкость счетчика или коэффициент счета — максимальное количество импульсов, которое может подсчитать счетчик.

По направлению счета счетчики разделяют на суммирующие,

вычитающие и реверсивные. В суммирующих счетчиках с каждым последующим импульсом увеличивается на единицу число, подсчитанное счетчиком. В вычитающих счетчиках с каждым последующим импульсом уменьшается на единицу число, подсчитанное счетчиком. Реверсивные счетчики могут работать как в режиме суммирования, так и вычитания, в зависимости от настроек схемы управления счетчика.

Простейшим счетчиком, коэффициент счета которого равен двум, является счетный триггер. Коэффициент счета (максимальное количество состояний, включая начальное)  $K_{\rm cq}$  связан с количеством триггеров m соотношением  $K_{\rm cq} \leq 2^k$ . Если  $K_{\rm cq} = 2^k$  ( $k \geq 0$ ), то счетчик относят к двоичным, а если  $K_{\rm cq} = 10^k$  (k > 0) — к десятичным. Существуют также счетчики с произвольным модулем счета N, для которых  $K_{\rm cq} = N^k$  (k > 0). Например, в устройствах счета времени используют счетчики, у которых N = 60.

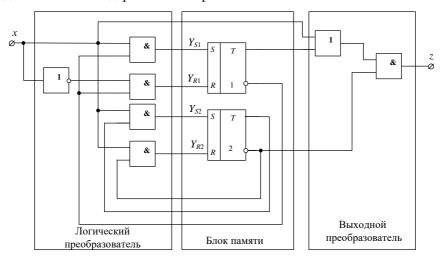

Быстродействие схемы счетчика определяется используемым переносом сигнала между разрядами. По способу переноса последовательным, параллельным различают счетчики c (комбинированным) переносом. счетчиках В последовательным переносом (асинхронных) сигнал передается последовательно с выхода триггера младшего разряда на вход триггера старшего разряда. В счетчиках с параллельным переносом (синхронных) информация передается одновременно всем триггерам. комбинированных счетчиках, используемых при больших коэффициентах счета, разряды разбиваются на группы, в которых реализуется параллельный перенос, между группами a последовательный.

В устройствах и системах автоматики, телемеханики и связи счетчики используют также при построении распределителей, преобразователей формы сигнала (совместно с мультиплексорами и демультиплексорами), при построении устройств отсчета интервалов времени, устройств избирания (совместно с дешифраторами и шифраторами) и ряде других.

Рассмотрим примеры построения различных типов счетчиков.

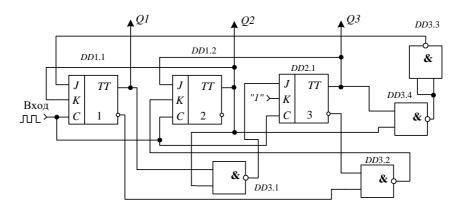

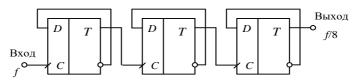

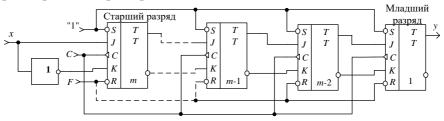

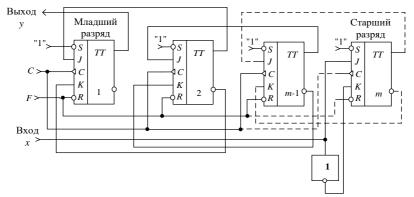

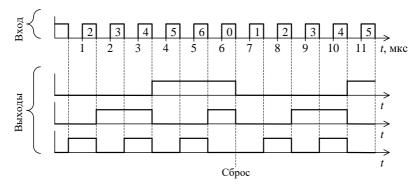

# 1.6.1 Счетчики с последовательным переносом

Наиболее просто строятся счетчики с последовательным переносом.

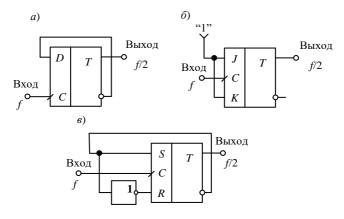

При этом триггеры счетчиков приводятся к счетным. Так D-триггер приводится к счетному соединением инверсного выхода со входом D, а счетным входом является вход C. Для включения JK-триггера в счетный режим соединяют вместе входы J и K и подают на них логическую единицу, а счетным входом является также вход C триггера.

При построении асинхронных счетчиков следует учитывать, как переключается используемый для их построения тип триггеров. Если триггеры переключаются по фронту входного импульса, то для построения суммирующего счетчика необходимо соединить инверсный выход каждого из младших разрядов (триггеров) со счетным входом старшего разряда, а для построения вычитающего счетчика соединяется со счетным входом старшего разряда прямой выход триггера младшего разряда.

В том случае, если применяются тригтеры с переключением по срезу входного импульса, то прямой и инверсный выходы тригтеров меняются местами при подключении по отношению к тому, как это выполняется для случая с тригтерами, переключающимися по фронту.

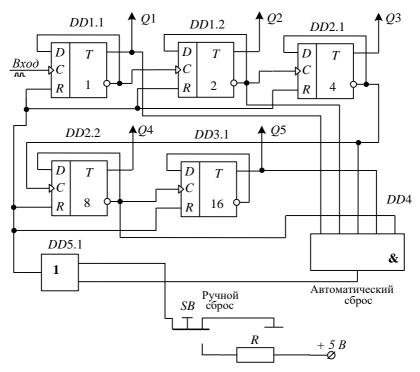

Пусть, например, требуется построить суммирующий счетчик с коэффициентом счета  $K_{\text{сч}}=17$  (счет ведется от 0 до 16) на D-триггерах, переключающихся по фронту входного импульса. Для построения счетчика требуется  $k=\inf[\log_2 K_{\text{сч}}]$  триггеров, где "int" обозначает ближайшее целое число, с округлением до целого числа в большую сторону. Также для определения количества триггеров на практике часто используют соотношение  $2^{k-l} \le K_{\text{сч}} \le 2^k$ . При  $K_{\text{сч}}=17$  получим  $k=\inf[\log_2 17]$  или  $2^{5-l} \le 17 \le 2^5$  (16 < 17 < 32), т.е. потребуется k=5 триггеров. Кроме того, при построении схемы счетчика следует учесть, что 5 триггеров позволяют обеспечить  $K_{\text{сч}}=32$  (от 0 до 31), а нам требуется только до 16. Поэтому в схему счетчика (рисунок 1.24) добавим узел автоматического сброса, срабатывающий при достижении числа 16.

Для того чтобы счетчик мог четко зафиксировать число шестнадцать, при определении условия сброса используется следующее за ним число семнадцать, т. е. конъюнкция  $Q5\overline{Q}4\overline{Q}3\overline{Q}2Q1$ , реализованная на элементе DD4. Кроме того, узел сброса дополним логическим элементом DD5.1 и кнопкой «SB», подключенной через ограничивающий резистор R. Использование

элемента DD5.1 позволяет по выбору осуществлять как автоматический сброс сигналом с элемента DD4, так и выполнить ручной сброс с помощью нажатия на кнопку «SB» и подачи, таким образом, сигнала логической единицы на входы сброса R триггеров счетчика.

Рисунок 1.24 — Схема суммирующего счетчика на *D*-тригтерах с коэффициентом счета 17

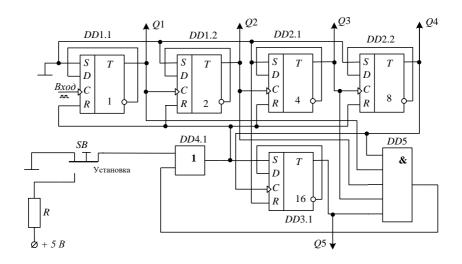

Если же нам необходимо построить счетчик при тех же условиях, но вычитающий, то схема изменится в части организации межтриггерных связей и схемы включения элементов управления. Для организации режима вычитания сигнал переноса будет подаваться на каждый из старших разрядов с прямого (а не инверсного, как у суммирующего счетчика) выхода триггера младшего разряда. Кроме того, нам необходимо реализовать схему установки (а не сброса, как у суммирующего счетчика) триггеров счетчика для получения того числа, от которого следует начать

вычитание. Поскольку некоторые триггеры потребуется устанавливать в единичное состояние, то используем такие триггеры, у которых, кроме входа сброса R, есть вход асинхронной установки S (рисунок 1.25).

При нажатии на кнопку установки "SB" на входы R первого, второго, третьего и четвертого триггеров и на вход S пятого триггера будет подана логическая единица. Это приведет к тому, что на выходах триггеров счетчика установится число шестнадцать, от которого и будет выполняться вычитание. Все незадействованные входы S и R триггеров подключаем к «земле» для обеспечения устойчивой работы счетчика. Подключение К представляющей собой логический нуль, неинверсных асинхронной установки триггеров делает их менее восприимчивыми к помехам. При этом также не произойдет нарушения алгоритма работы триггеров, так как по асинхронным входам они управляются логической единицей, а не логическим нулем.

реализована образом, Схема счетчика таким после достижения числа «нуль» (когда все триггеры установились в нуль), со следующим входным импульсом все триггеры переключатся в единицу и счетчик окажется в состоянии 31. Однако это нам не требуется, поскольку  $K_{cy}$  в таком случае будет равен 32, а не 17. Поэтому схему управления следует дополнить логическим элементом DD5, который будет отслеживать число 31 (конъюнкция 0102030405) и выполнять автоматическую переустановку счетчика в число 16 для обеспечения  $K_{cq} = 17$ .

Рисунок 1.25 — Схема вычитающего счетчика на D-триггерах с коэффициентом счета 17

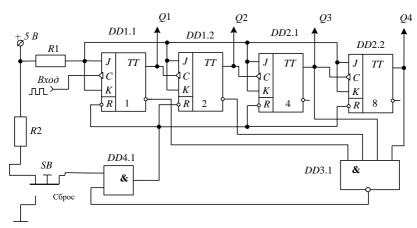

Реализуем схему асинхронного суммирующего счетчика с  $K_{\text{сч}} = 12$  на JK-триггерах, переключающихся по срезу (рисунок 1.26). Для обеспечения требуемого  $K_{\text{сч}}$  необходимо  $k = \inf[\log_2 12] = 4$  триггера.

Рисунок 1.26 — Схема суммирующего счетчика на *JK*-тригтерах с коэффициентом счета, равным двенадцати

Включим триггеры в счетный режим, соединив вместе входы J и K и подав на них логическую единицу. Поскольку триггеры двухступенчатые и переключаются по срезу, то для организации

режима суммирования необходимо соединять прямые выходы младших триггеров со счетными входами триггеров старших разрядов. Схема управления счетчиком состоит из кнопки ручного сброса SB, логического элемента DD3.1, вычисляющего сигнал автоматического сброса по достижении числа двенадцать (согласно  $K_{\text{сч}}$ ) и элемента увязки DD4.1, выбирающего режим сброса (ручной или автоматический).

Хотя счетчики с последовательным переносом легко синтезируются и обладают схемной простотой, они являются относительно медленнодействующими. В таких счетчиках сигнал переключения (переноса) прежде чем дойдет до i-го разряда должен пройти через (i-1) разряд, что накладывает ограничение на интервал между соседними входными импульсами. Этот интервал должен быть больше, чем  $t_{\rm n}(k-1)$ , где  $t_{\rm n}$  — время переключения триггера, k — количество триггеров (разрядов) схемы счетчика.

Другой недостаток асинхронных счетчиков заключается в том, что в ходе переключения младшие разряды принимают новые состояния, в то время как старшие еще находятся в прежнем. Из-за этого счетчик при смене одного числа другим проходит ряд промежуточных состояний, каждое из которых может быть принято за код числа пришедших на вход счетчика импульсов.

В том случае, когда для дискретной системы, в которую входит асинхронный счетчик, отмеченные недостатки являются существенными, используют синхронный счетчик.

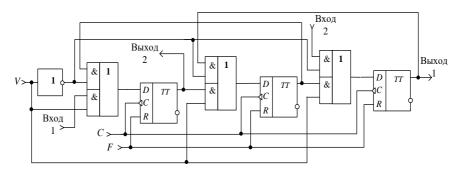

# 1.6.2 Счетчики с параллельным переносом

В отличие от асинхронных в синхронных счетчиках ко всем разрядам информация о состоянии предыдущих разрядов поступает параллельно так же, как и входные (подсчитываемые) импульсы. Триггеры счетчиков с параллельным переносом переключаются, вследствие этого, одновременно. Из-за того, что необходимо обеспечивать одновременность переключений разрядов синхронных счетчиков, логические цепи между триггерами усложнены и процесс синтеза синхронных счетчиков более трудоемок по сравнению с процессом синтеза асинхронных счетчиков. Рассмотрим примеры.

Построим суммирующий счетчик с параллельным переносом на JK-триггерах и  $K_{\text{сч}}=7$ . Логические связи между триггерами

реализуем в базисе «И-НЕ».

Для синтеза данного счетчика необходимо построить таблицу истинности, в которую включаются столбцы текущих и последующих состояний триггеров счетчика, столбцы определения функций возбуждения (вызывающих переключения) триггеров и столбец номера входного импульса. Количество триггеров счетчика определяется по той же формуле, что и для асинхронных счетчиков.

Заполнение столбцов функций возбуждения триггеров осуществляется на основе таблицы переходов JK-триггера (таблица 1.16).

Таблица 1.16 – Таблица переходов ЈК-триггера

| Изменение сигнала на выходе <i>Q</i> | Что подать на вход $J$ | Что подать на вход $K$ |

|--------------------------------------|------------------------|------------------------|

| $0 \rightarrow 0$                    | 0                      | ~                      |

| $0 \rightarrow 1$                    | 1                      | ~                      |

| $1 \rightarrow 0$                    | ~                      | 1                      |

| $1 \rightarrow 1$                    | ~                      | 0                      |

Количество триггеров для  $K_{\rm cq}=7$  будет равно  $k={\rm int}[\log_2 7]=3$ . Заполним таблицу истинности счетчика (таблица 1.17). В последней строке таблицы зададим переход триггеров в исходные (нулевые) состояния, что равносильно автоматическому сбросу счетчика.

Таблица 1.17 — Таблица истинности счетчика с  $K_{cq} = 7$  на JK-триггерах

| Номер<br>входного | Текущие состояния триггеров |    |            | Последующие состояния триггеров |    |            | Функции возбуждения |            |            |            |            |            |

|-------------------|-----------------------------|----|------------|---------------------------------|----|------------|---------------------|------------|------------|------------|------------|------------|

| импульса          | Q1                          | Q2 | <i>Q</i> 3 | Q1                              | Q2 | <i>Q</i> 3 | <i>J</i> 1          | <i>K</i> 1 | <i>J</i> 2 | <i>K</i> 2 | <i>J</i> 3 | <i>K</i> 3 |

| 0                 | 0                           | 0  | 0          | 0                               | 0  | 1          | 0                   | ~          | 0          | ~          | 1          | ~          |

| 1                 | 0                           | 0  | 1          | 0                               | 1  | 0          | 0                   | ~          | 1          | ~          | ~          | 1          |

| 2                 | 0                           | 1  | 0          | 0                               | 1  | 1          | 0                   | ~          | ~          | 0          | 1          | ~          |

| 3                 | 0                           | 1  | 1          | 1                               | 0  | 0          | 1                   | ~          | ~          | 1          | ~          | 1          |

| 4                 | 1                           | 0  | 0          | 1                               | 0  | 1          | ~                   | 0          | 0          | ~          | 1          | ~          |

| 5                 | 1                           | 0  | 1          | 1                               | 1  | 0          | ~                   | 0          | 1          | ~          | ~          | 1          |

| 6                 | 1                           | 1  | 0          | 0                               | 0  | 0          | ~                   | 1          | ~          | 1          | 0          | ~          |

Поскольку счетчик должен быть суммирующим, то в столбце с номером входного импульса десятичное число все время увеличивается на единицу. Столбцы текущих состояний показывают

код десятичного числа в столбце с номером входного импульса, а столбцы последующих состояний показывают увеличенный на единицу код десятичного числа столбца с номером входного импульса. По сути таблицу истинности строят для определения функций возбуждения J и K триггеров таким образом, чтобы они вызвали реализацию триггерами алгоритма суммирования в двоичной интерпретации. После того как текущие и последующие состояния триггеров заполнены, приступают к определению функций  $J_i$  и  $K_i$  для каждого из триггеров счетчика.

Для каждой строки таблицы истинности смотрим, как должны переключаться из текущего состояния в последующее триггеры Q1, Q2 и Q3 в отдельности и соответственно этим переключениям проставляем значения соответствующих им функций J1, K1; J2, K2 и J3, K3 по таблице 1.16. Так для первой строки таблицы истинности имеем: Q1 должен остаться в нулевом состоянии  $(0 \to 0)$ , тогда получаем, что J1 = 0 и  $K1 = \sim$ ; Q2 должен также остаться в нулевом состоянии  $(0 \to 0)$ , тогда J2 = 0 и  $K2 = \sim$ ; Q3 должен перейти в единичное состояние  $(0 \to 1)$ , тогда J3 = 1 и  $K3 = \sim$ .

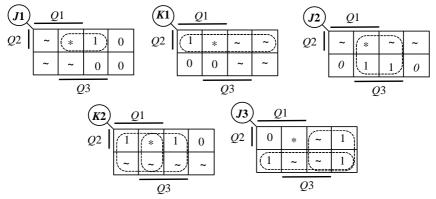

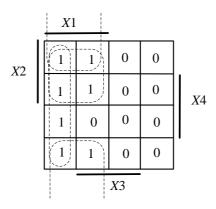

После заполнения таблицы истинности выполняем упрощение функций  $J_i$  и  $K_i$  с учетом того, что эти функции заданы частично (кроме того, что есть безразличные состояния входов триггеров «~», существует также незадействованное состояние «\*»:  $Q1=1,\ Q2=1,\ Q3=1,\$ в которое счетчик по алгоритму не попадет). Учитывая, что для функции K3 в таблице истинности нет нулей, можно сразу записать K3=1. Остальные функции упростим при помощи карт Карно (рисунок 1.27). Адресные переменные для карт — текущие состояния триггеров счетчика.

$$J1 = Q2Q3$$

;  $K1 = Q2$ ;  $J2 = Q3$ ;  $K2 = Q1 \lor Q3$ ;  $J3 = \overline{Q}1 \lor \overline{Q}2$ .

Рисунок 1.27 – Упрощение функций суммирующего счетчика с коэффициентом счета семь на *JK*-триггерах

Преобразуем полученные функции к базису «И-HE», используя законы двойного отрицания и двойственности:  $J1 = \overline{Q2} \, \overline{Q3} = \overline{Q2} \, | \, \overline{Q3}$ ;  $K2 = \overline{\overline{Q1}} \, \overline{\overline{Q3}} = \overline{Q1} \, | \, \overline{Q3}$ ;  $J3 = \overline{Q1} \, Q\overline{2} = Q1 \, | \, Q2$ . Схема счетчика приведена на рисунке 1.28.

Поскольку в таблице истинности был задан переход счетчика в исходное состояние при достижении им максимального числа счета, то не требуется и специальная схема сброса. Однако, так как счетчики являются составными частями более сложных дискретных устройств, то должна присутствовать возможность их произвольного сброса согласованно с остальными частями общей схемы дискретного устройства. Поэтому в схему счетчика добавляют в таких случаях и узел сброса, задействовав входы R асинхронной установки триггеров в нуль. Выполняется этот этап по аналогии с построением схем управления асинхронных счетчиков (на рисунке 1.28 узел сброса не представлен).

Построим вычитающий счетчик на D-триггерах с параллельным переносом и  $K_{\rm cu}=11$ . Логические связи между триггерами реализуем в базисе «ИЛИ-НЕ».

Рисунок 1.28 – Схема суммирующего счетчика с коэффициентом счета семь на *JK*-триггерах

Методика синтеза счетчика на D-триггерах отличается от методики синтеза счетчика на JK-триггерах использованием таблицы переходов для D-триггера (таблица 1.18). Поскольку счетчик должен быть вычитающим, то в столбце с номером входного импульса десятичное число все время уменьшается на единицу, начиная от значения ( $K_{\text{сч}} - 1$ ), т.е. от десяти.

Столбцы текущих состояний в таблице истинности счетчика (таблица 1.19) показывают код десятичного числа в столбце с номером входного импульса, а столбцы последующих состояний — уменьшенный на единицу код десятичного числа столбца с номером входного импульса.

Таблица 1.18 - Таблица переходов *D*-триггера

| Изменение сигнала | Что подать на вход | Изменение сигнала | Что подать на вход |

|-------------------|--------------------|-------------------|--------------------|

| на выходе $Q$     | D                  | на выходе $Q$     | D                  |

| $0 \rightarrow 0$ | 0                  | $1 \rightarrow 0$ | 0                  |

| $0 \rightarrow 1$ | 1                  | $1 \rightarrow 1$ | 1                  |

Для построения счетчика необходимо  $k=\inf[\log_2 11]=4$  триггера. Таблицу истинности составляют с целью определения функций возбуждения  $D_i$  триггеров таким образом, чтобы они вызвали реализацию триггерами алгоритма вычитания в двоичном эквиваленте. После того как текущие и последующие состояния триггеров заполнены, приступают к определению функций  $D_i$  каждого триггера счетчика.

Таблица 1.19 — Таблица истинности вычитающего счетчика с  $K_{cq} = 11$  на D-триггерах

|          | na D-1 phi 1 c pax |       |        |            |                     |        |      |    |             |    |    |    |

|----------|--------------------|-------|--------|------------|---------------------|--------|------|----|-------------|----|----|----|

| Номер    |                    | Теку  | лцие   |            | I                   | Тослед | ующи | е  | Функции     |    |    |    |

| входного | COCT               | пинко | тригго | еров       | состояния триггеров |        |      |    | возбуждения |    |    |    |

| импульса | <i>Q</i> 1         | Q2    | Q3     | <i>Q</i> 4 | Q1                  | Q2     | Q3   | Q4 | <i>D</i> 1  | D2 | D3 | D4 |

| 10       | 1                  | 0     | 1      | 0          | 1                   | 0      | 0    | 1  | 1           | 0  | 0  | 1  |

| 9        | 1                  | 0     | 0      | 1          | 1                   | 0      | 0    | 0  | 1           | 0  | 0  | 0  |

| 8        | 1                  | 0     | 0      | 0          | 0                   | 1      | 1    | 1  | 0           | 1  | 1  | 1  |

| 7        | 0                  | 1     | 1      | 1          | 0                   | 1      | 1    | 0  | 0           | 1  | 1  | 0  |

| 6        | 0                  | 1     | 1      | 0          | 0                   | 1      | 0    | 1  | 0           | 1  | 0  | 1  |

| 5        | 0                  | 1     | 0      | 1          | 0                   | 1      | 0    | 0  | 0           | 1  | 0  | 0  |

| 4        | 0                  | 1     | 0      | 0          | 0                   | 0      | 1    | 1  | 0           | 0  | 1  | 1  |

| 3        | 0                  | 0     | 1      | 1          | 0                   | 0      | 1    | 0  | 0           | 0  | 1  | 0  |

| 2        | 0                  | 0     | 1      | 0          | 0                   | 0      | 0    | 1  | 0           | 0  | 0  | 1  |

| 1        | 0                  | 0     | 0      | 1          | 0                   | 0      | 0    | 0  | 0           | 0  | 0  | 0  |

| 0        | 0                  | 0     | 0      | 0          | 1                   | 0      | 1    | 0  | 1           | 0  | 1  | 0  |

Анализируя данные таблицы 1.19, легко заметить, что значения функций возбуждения совпадают с теми значениями выходов триггеров, в которые они должны переключиться, что облегчает заполнение подобных таблиц в последующем.

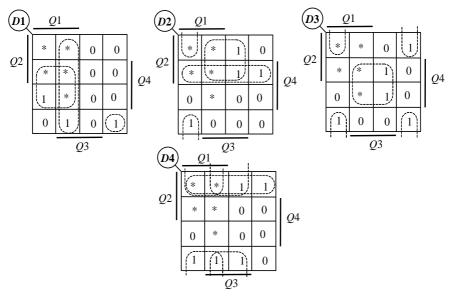

Выполним упрощение функций возбуждения триггеров с помощью карт Карно (рисунок 1.29) с учетом того, что наборы 11 — 15 не используются в таблице истинности, и поэтому упрощаемые функции заданы частично.

В результате упрощения получим:

$$D1 = Q1Q3 \lor Q1Q4$$

;  $D2 = Q2Q4 \lor Q2Q3 \lor Q1\overline{Q}3\overline{Q}4$ ;  $D3 = Q3Q4 \lor \overline{Q}3\overline{Q}4$ ;  $D4 = Q2\overline{Q}4 \lor Q3\overline{Q}4 \lor Q1\overline{Q}4$ . Преобразуем полученные функции к виду, удобному для представления в базисе «ИЛИ-НЕ» с помощью закона

двойного

отрицания:

$$D1 = \overline{\overline{Q1} \vee \overline{Q3} \vee \overline{Q1} \vee \overline{Q4}} = \overline{(\overline{Q1} \vee \overline{Q3}) \vee (\overline{Q1} \vee \overline{Q4})},$$

$$D2 = \overline{(\overline{Q2} \vee \overline{Q4}) \vee (\overline{Q2} \vee \overline{Q3}) \vee (\overline{Q1} \vee Q3 \vee Q4)}, D3 = \overline{(\overline{Q3} \vee \overline{Q4}) \vee (Q3 \vee Q4)},$$

$$D4 = \overline{(\overline{Q2} \vee Q4) \vee (\overline{Q3} \vee Q4) \vee (\overline{Q1} \vee Q4)}.$$

закона

двойственности

Так как в таблице истинности для D-триггера нет безразличных состояний для триггеров, поэтому функции возбуждения получаются более сложными.

В схеме вычитающего счетчика необходимо предусмотреть установку его триггеров в то число, от которого выполняется вычитание, согласно таблице истинности. В рассматриваемом случае

- это число  $K_{\text{сч}}=11-1=10.$  Схема счетчика представлена на рисунке 1.30. Поскольку функции  $D_i$  относительно сложны, используем вариант построения схемы счетчика с общей шиной.

Рисунок 1.29 — Упрощение функций вычитающего счетчика на D-триггерах с  $K_{\text{сч}}=11$

В тех случаях, когда необходимо синтезировать счетчики с параллельным переносом и большим  $K_{\text{сч}}$ , строят таблицы истинности большим количеством строк. В таких таблицах сложно ориентироваться, работа с ними отнимает много времени. Поэтому в используют компромиссный вариант - применение ряде случаев смешанным (параллельносчетчиков co переносом последовательным). Некоторые варианты счетчиков таких рассмотрены ниже.

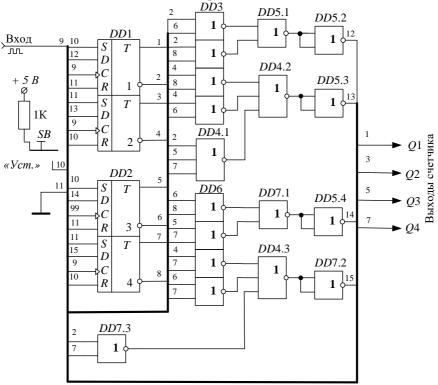

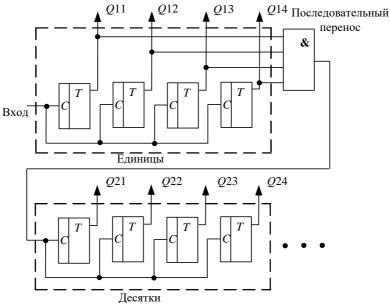

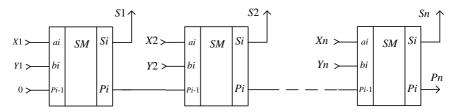

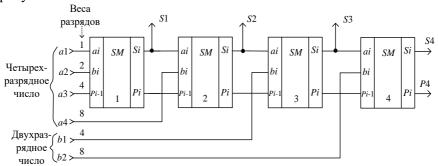

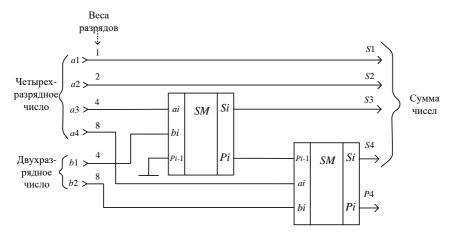

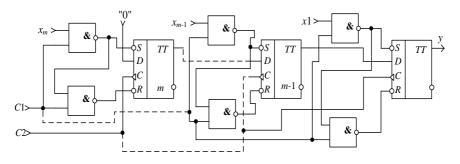

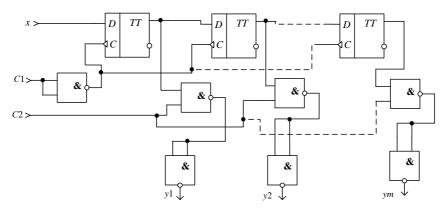

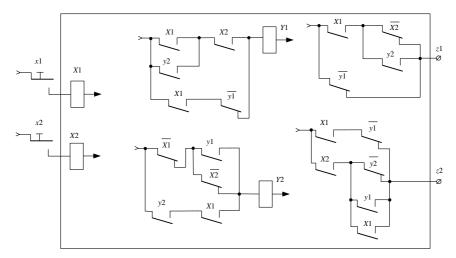

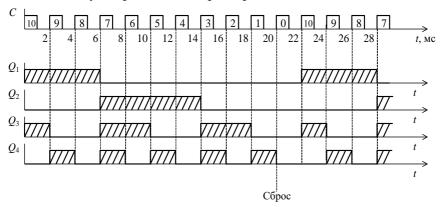

## 1.6.3 Счетчики с параллельно-последовательным переносом

В счетчиках со смешанным переносом используется двоичнодесятичный принцип счета (рисунок 1.31). При этом каждому десятичному числу соответствует свой двоичный счетчик с  $K_{\rm cq}=10$ . Внутри каждой декады производится параллельный, а между декадами – последовательный перенос.

Рисунок 1.30 — Схема вычитающего счетчика на D-триггерах с  $K_{cq} = 11$

Так как счетчики всех декад имеют  $K_{\rm cч}=10$ , то в этом случае таблица истинности будет одна (реже — две, когда самая старшая декада имеет  $K_{\rm cч}<10$ ).

Особенностью двоично-десятичных счетчиков является то, что при синтезе их схемы всегда требуется схема сброса/установки (за исключением тех случаев, когда  $K_{\rm cq}$  кратен 10), поскольку в таблице истинности не задается согласованный сброс декад.

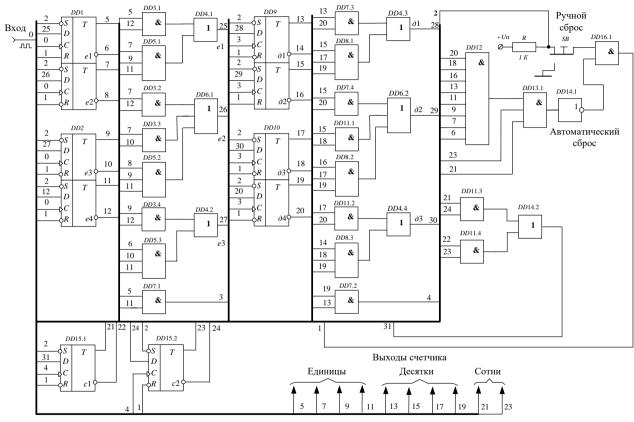

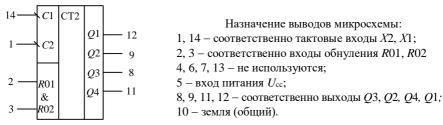

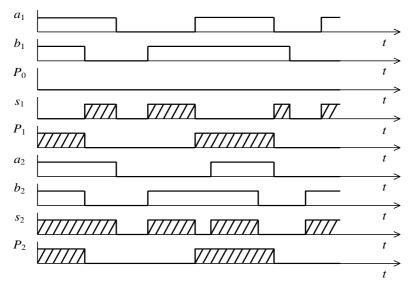

Пусть требуется построить двоично-десятичный суммирующий счетчик с  $K_{\text{сч}} = 387$  на D-триггерах. Счетчик имеет три декады: сотни, десятки и единицы. При этом  $K_{\text{сч}}$  самой старшей декады равен 4 (что меньше десяти), поэтому для этой декады будем использовать отдельную таблицу истинности. Это делается с целью экономии триггеров (для  $K_{\text{сч}} = 10$  требуется 4 триггера, а для  $K_{\text{сч}} = 4$  – два). Для

десятков и единиц потребуется общая таблица истинности (таблица 1.20). Она полностью подобна таблице истинности обычного суммирующего счетчика с параллельным переносом.

Рисунок 1.31 – Принцип построения двоично-десятичных счетчиков

Таблица 1.20 — Таблица истинности единиц и десятков суммирующего счетчика на D-триггерах с  $K_{cq} = 387$

| Номер    | Te | екущее о<br>триг | состоян: | ие | Посл       | едующо<br>тригі | ее состо | яние | Функции возбуждения |    |    |    |

|----------|----|------------------|----------|----|------------|-----------------|----------|------|---------------------|----|----|----|

| импульса | Q1 | Q2               | Q3       | Q4 | <i>Q</i> 1 | Q2              | Q3       | Q4   | D1                  | D2 | D3 | D4 |

| 0        | 0  | 0                | 0        | 0  | 0          | 0               | 0        | 1    | 0                   | 0  | 0  | 1  |

| 1        | 0  | 0                | 0        | 1  | 0          | 0               | 1        | 0    | 0                   | 0  | 1  | 0  |

| 2        | 0  | 0                | 1        | 0  | 0          | 0               | 1        | 1    | 0                   | 0  | 1  | 1  |

| 3        | 0  | 0                | 1        | 1  | 0          | 1               | 0        | 0    | 0                   | 1  | 0  | 0  |

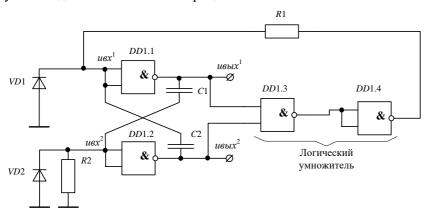

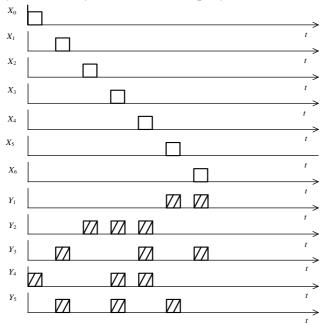

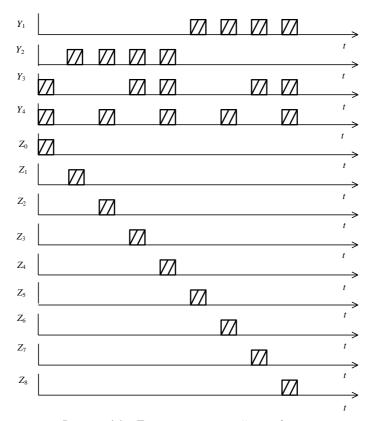

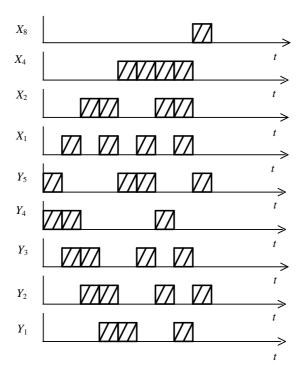

| 4        | 0  | 1                | 0        | 0  | 0          | 1               | 0        | 1    | 0                   | 1  | 0  | 1  |