5 Обнаружение неисправностей в самопроверяемых комбинационных схемах с использованием свойств самодвойственных функций / М. Гессель, В. И. Мошанин, В. В. Сапожников, Вл. В. Сапожников // Автоматика и телемеханика. – 1997. – № 12. – С. 193–200.

6 **Ефанов, Д. В.** Тестеры самодвойственных и «близких» к ним сигналов / Д. В. Ефанов, Д. В. Пивоваров // Известия высших учебных заведений. Приборостроение. – 2024. – Т. 67, № 1. – С. 5–19. – DOI: 10.17586/0021-3454-2024-67-1-5-19.

7 Self-Dual Complement Method up to Constant-Weight Codes for Arrangement of Combinational Logical Circuits Concurrent Error-Detection Systems / D. Efanov, V. Sapozhnikov, VI. Sapozhnikov [et al.] // Proceedings of 17th IEEE East-West Design & Test Symposium (EWDTs'2019), Batumi, Georgia, September 13–16, 2019. – Р. 136–143. – DOI: 10.1109/EWDTs.2019.8884398.

8 Обнаружение неисправностей в комбинационных схемах на основе самодвойственного дополнения до равновесных кодов / Д. В. Ефанов, В. В. Сапожников, Вл. В. Сапожников, Д. В. Пивоваров // Труды Института системного программирования РАН. – 2019. – Т. 31, № 1. – С. 115–132. – DOI: 10.15514/ISPRAS-2019-31(1)-8.

9 The On-Line Encyclopedia of Integer Sequences (OEIS). – URL: <https://oeis.org/> (дата обращения: 20.01.2025).

10 **Lala, P. K.** Self-Checking and Fault-Tolerant Digital Design / P. K. Lala. – San Francisco : Morgan Kaufmann Publishers, 2001. – 216 р.

11 Построение самопроверяемых комбинационных схем на основе свойств самодвойственных функций / М. Гессель, А. А. Морозов, В. В. Сапожников, Вл. В. Сапожников // Автоматика и телемеханика. – 2000. – № 2. – С. 151–163.

12 **Efanov, D. V.** Investigation of Ways of Synthesizing Concurrent Error-Detection Circuits Based on Boolean Signal Correction Using Uniform Separable Codes / D. V. Efanov, Y. I. Yelina // Russian Microelectronics. – 2024. – Vol. 53, № 5. – Р. 471–482. – DOI: 10.1134/S1063739724600456.

13 Checkability of the Digital Components in Safety-Critical Systems: Problems and Solutions / A. Drozd, V. Kharchenko, S. Antoshchuk [et al.] // Proceedings of 9th IEEE East-West Design & Test Symposium (EWDTs'2011), Sevastopol, 2011. – Р. 411–416. – DOI: 10.1109/EWDTs.2011.6116606.

14 **Сапожников, Вл. В.** Синтез систем управления движением поездов на железнодорожных станциях с исключением опасных отказов / Вл. В. Сапожников. – М. : Наука, 2021. – 229 с.

УДК 004.052.32+681.518.5

## МЕТОДИКА СИНТЕЗА САМОКВАЗИДВОЙСТВЕННЫХ ДИСКРЕТНЫХ УСТРОЙСТВ С КОНТРОЛЕМ ВЫЧИСЛЕНИЙ ПО ДВУМ ДИАГНОСТИЧЕСКИМ ПРИЗНАКАМ

Д. В. ЕФАНОВ

Санкт-Петербургский политехнический университет Петра Великого, Российская Федерация

Российский университет транспорта (МИИТ), г. Москва

Ташкентский государственный транспортный университет, Республика Узбекистан

Развитие технологий синтеза дискретных устройств и систем управления ответственными технологическими процессами, несомненно, связано и с параллельным совершенствованием области технической диагностики. Особую значимость теоретические исследования принимают при создании новой элементной базы или развитии малоизученных компонентов. Например, так дело обстоит в исследовании особенностей квантовых вычислений [1, 2]. Поэтому важно не только разрабатывать новые методы построения и реализации дискретных устройств с высокими показателями надежности и безопасности, но и продумывать и исследовать методы наделения их структур свойствами контролепригодности, самопроверяемости и отказоустойчивости. Центральным вопросом здесь оказывается возможность создания устройства с оперативным обнаружением неисправностей [3, 4].

Исследования автора показали, что при синтезе дискретных устройств с обнаружением неисправностей можно использовать сразу же два и более диагностических признака для контроля вычислений [5]. При этом структурная избыточность схемы встроенного контроля увеличивается незначительно за счет довольно простых контрольных устройств, а наблюдаемость ошибок на контрольных выходах возрастает на 25–40 % в зависимости от структуры объекта диагностирования и условий трансляции ошибок, вызываемых неисправностями, на его выходы [6].

При синтезе дискретных устройств с обнаружением неисправностей по двум и более диагностическим признакам оказывается эффективным использование логической коррекции сигналов (ЛКС), впервые описанной в [7] под названием «логическое дополнение». Особое место здесь имеют равновесные коды « $r$  из  $n$ » ( $r/n$ -коды), где  $r$  и  $n$  – вес кодового слова и его длина. Довольно легко синтезируется схема встроенного контроля (СВК) по кодам вида  $r/2r$ , например 2/4, 3/6 и т. д. В [8] предложено использовать такие коды при синтезе СВК с контролем вычислений по признакам при-

надлежности кодовых слов, формируемых в СВК, равновесным кодам вида  $r/2r$ , а также самодвойственности каждой функции, определяющей значения разрядов кодовых слов этого кода на каждом наборе значений аргументов. За счет простоты схемы сжатия самодвойственных сигналов [9] и тестера самодвойственности [5] удается строить более эффективную СВК, чем при контроле вычислений только по одному диагностическому признаку. Дальнейшие исследования показали, что возможен контроль не только самодвойственности каждой функции, описывающей разряды кодовых слов, но и так называемой самоквазидвойственности [10]. Самоквазидвойственность функции подразумевает равенство ее значений на ортогональных по всем переменным наборах значений аргументов. Покажем, как в случае контроля еще и этого диагностического признака эффективно применять равновесные коды.

При синтезе СВК по двум диагностическим признакам – принадлежности кодовых слов  $r/n$ -коду и самоквазидвойственности каждой функции, описывающей разряды кодовых слов, – эффективным оказывается использование 1/4-кодов. Данные коды имеют всего четыре рабочих кодовых слова  $\{0001, 0010, 0100, 1000\}$ . Тестеры данных кодов – одни из самых простых тестеров равновесных кодов [11]. Для полной проверки их относительно одиночных константных неисправностей требуется подача всех четырех кодовых слов (это минимально возможное количество тестовых комбинаций для тестеров в принципе).

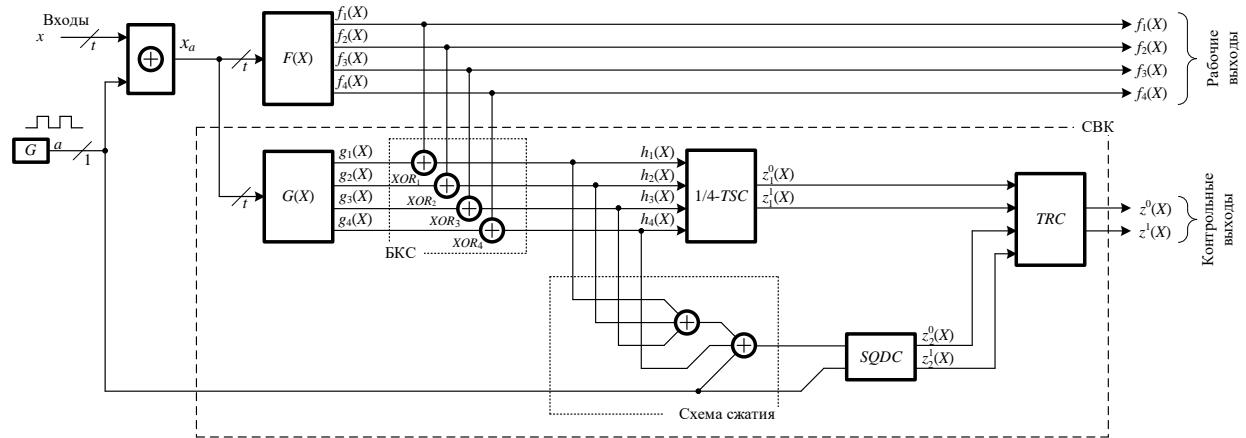

Базовая структура организации контроля вычислений представлена на рисунке 1. В ней блок  $F(X)$  является объектом диагностирования и формирует булевые векторы  $\langle f_4(X) f_3(X) f_2(X) f_1(X) \rangle$  на каждом наборе значений аргументов  $\langle X \rangle = \langle x_t x_{t-1} \dots x_2 x_1 \rangle$ . В СВК каждый вектор  $\langle f_4(X) f_3(X) f_2(X) f_1(X) \rangle$  преобразуется в вектор  $\langle h_4(X) h_3(X) h_2(X) h_1(X) \rangle$  за счет использования функций ЛКС  $g_1(X), g_2(X), g_3(X), g_4(X)$ , вычисляемых блоком  $G(X)$ . Преобразования осуществляются в блоке коррекции сигналов (БКС) по формуле  $h_j(X) = f_j(X) \oplus g_j(X), j = \overline{1, 4}$ . Преобразования выполняются так, чтобы вектор  $\langle h_4(X) h_3(X) h_2(X) h_1(X) \rangle$  на каждом наборе значений аргументов принадлежал 1/4-коду и каждая функция  $h_j(X)$  была самоквазидвойственной. Для контроля вычислений устанавливается тестер 1/4-кода (1/4-TSC), схема сжатия самоквазидвойственных сигналов и тестер самоквазидвойственности SQDC [12]. Сигналы с выходов с двух подсхем контролла сжимаются на входах самопроверяемого модуля сжатия парофазных сигналов TRC [5, 6, 11].

Рисунок 1 – Базовая структура организации СВК

Представленная на рисунке 1 структура работает в импульсном режиме, когда сигналы логического 0 и логической 1 подаются в виде последовательностей импульсов – 0101...01 и 1010...10 соответственно. Для этого используется генератор  $G$  импульсов  $a$  со скважностью 2, а сигнал с каждого входа объекта диагностирования представляется в виде последовательности с помощью двухвходового элемента сложения по модулю 2: на первый вход его подается сигнал с определенного входа, а на второй – сигнал  $a$  с генератора.

Для организации контроля вычислений выделяются комбинационные составляющие в структурах объектов диагностирования. Определяется общее количество  $n$  выходов. Выходы разбиваются

на  $q = \left\lfloor \frac{n}{4} \right\rfloor$  подмножеств мощностью 4 без пересечений и, возможно (при  $n \pmod 4 \neq 0$ ), еще на одно

подмножество, где имеется  $n \pmod 4$  выходов и  $(4 - n \pmod 4)$  уже использованных в других выделенных четверках. Для каждой четверки выходов строится отдельная подсхема контроля вычислений по двум диагностическим признакам с использованием 1/4-кода с применением следующих правил:

1 Наборы значений аргументов разбиваются на пары, соответствующие десятичным эквивалентам двоичных представлений наборов, – пары  $(i, 2^t - 1 - i)$ ,  $i \in \{0, 1, \dots, 2^{t-1} - 1\}$ , где  $t$  – число входов.

2 Наборы  $i$ ,  $i \in \{0, 1, \dots, 2^{t-1} - 1\}$ , в лексикографическом порядке следования разбиваются на четыре группы по  $\frac{2^{t-1}}{4} = 2^{t-3}$  набора в каждой.

3 Каждой полученной группе приписывается одно из кодовых слов 1/4-кода: {0001, 0010, 0100, 1000}.

4 Наборам с номерами  $2^t - 1 - i$  приписываются те же кодовые слова 1/4-кода, что и наборам  $i$ .

5 Определяются значения функций логической коррекции  $g_1(X)$ ,  $g_2(X)$ ,  $g_3(X)$ ,  $g_4(X)$ .

Далее СВК строится в выбранном элементном базисе.

Представленный подход к синтезу СВК на основе ЛКС с применением 1/4-кода подходит для использования с любыми комбинационными составляющими без ограничений на виды реализуемых ими булевых функций. Подход абсолютно новый и ранее не исследовался учеными и инженерами, поэтому требует многочисленных экспериментов и тестирования на реальных объектах, обеспечивающих автоматическое протекание технологических процессов в различных секторах экономики. Предварительные теоретические выкладки показывают его высокую эффективность в части обнаружения ошибок на выходах комбинационных составляющих дискретных устройств.

#### Список литературы

1 Deductive Matrix Synthesis for Fault Simulation / W. Gharibi, V. Hahanov, D. Devadze [et al.] // 2023 17th International Conference on the Experience of Designing and Application of CAD Systems (CADSM), 22–25 February 2023, Jaroslaw, Poland. – DOI: 10.1109/CADSM58174.2023.10076506.

2 Vector Synthesis of Fault Testing Map for Logic / V. Hahanov, W. Gharibi, S. Chumachenko, E. Litvinova // IAES International Journal of Robotics and Automation (IJRA). – 2024. – Vol. 13, is. 3. – P. 293–306. – DOI: 10.11591/ijra.v13i3.pp293-306.

3 Сапожников, В. В. Дискретные автоматы с обнаружением отказов / В. В. Сапожников, Вл. В. Сапожников. – Л. : Энергоатомиздат, Ленингр. отд., 1984. – 112 с.

4 Согомонян, Е .С. Самопроверяемые устройства и отказоустойчивые системы / Е. С. Согомонян, Е. В. Слабаков. – М. : Радио и связь, 1989. – 208 с.

5 Ефанов, Д. В. Исследование свойств самодвойственных комбинационных устройств с контролем вычислений на основе кодов Хэмминга / Д. В. Ефанов, Т. С. Погодина // Информатика и автоматизация. – 2023. – Т. 22, № 2. – С. 349–392. – DOI: 10.15622/ia.22.2.5.

6 Combinational Circuits Testing Based on Hsiao Codes with Self-Dual Check Functions / D. V. Efanov, T. S. Pogodina, N. M. Aripov [et al.] // Computation. – 2025. – Vol. 13, is. 1. – 15 p. – DOI: 10.3390/computation13010015.

7 Организация функционального контроля комбинационных схем методом логического дополнения / В. В. Сапожников, Вл. В. Сапожников, А. В. Дмитриев [и др.] // Электронное моделирование. – 2002. – Т. 24, № 6. – С. 52–66.

8 Self-Dual Complement Method up to Constant-Weight Codes for Arrangement of Combinational Logical Circuits Concurrent Error-Detection Systems / D. Efanov, V. Saposhnikov, Vl. Saposhnikov [et al.] // Proceedings of 17th IEEE East-West Design & Test Symposium (EWDTS'2019), Batumi, Georgia, September 13–16, 2019. – P. 136–143. – DOI: 10.1109/EWDTS.2019.8884398.

9 New Self-Dual Circuits for Error Detection and Testing / A. Dmitriev, V. Saposhnikov, Vl. Saposhnikov, M Goessel // VLSI Design. – 2000. – Vol. 11, is. 1. – P. 1–21. – DOI: 10.1155/2000/84720.

10 Ефанов, Д. В. Синтез самопроверяемых дискретных устройств на основе полиномиальных кодов с контролем вычислений по нескольким диагностическим признакам / Д. В. Ефанов, Д. В. Пивоваров // Автоматика и телемеханика. – 2025. – № 5. – С. 39–60. – DOI: 10.31857/S0005231025050036. – EDN: AXPIOQ.

11 Сапожников, В. В. Самопроверяемые дискретные устройства / В. В. Сапожников, Вл. В. Сапожников. – СПб. : Энергоатомиздат, 1992 – 224 с.

12 Ефанов, Д. В. Особенности использования кодов Хэмминга при синтезе самопроверяемых цифровых устройств на основе метода инвертирования данных / Д. В. Ефанов // Известия высших учебных заведений. Электроника. – 2024. – Т. 29, № 3. – С. 379–392. – DOI: 10.24151/1561-5405-2024-29-3-379-392.